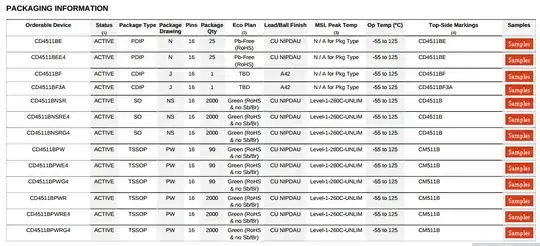

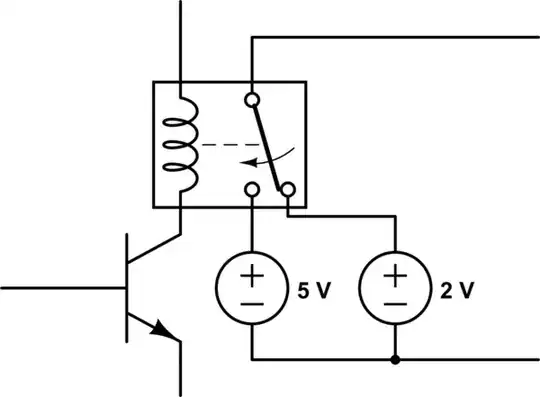

This circuit:

doesn't make much sense. Due to the positive feedback, it has two possible stable states.

In one stable state, the transistor is fully off. That means the negative input of the opamp is at 5 V. Since the positive input is always at 2 V, this drives the opamp output as low as it can go. Since you said to analyze like the opamp were ideal, that means the output will go to 0. This holds the transistor off. This state is therefore indeed stable.

The other possible stable state is when the opamp negative input is below 2 V. That would drive the output high, which would keep the transistor on. However, with this being a ideal opamp, the output would go to the positive supply. You haven't said what that is, so I'll assume it's the same 5 V the rest of the circuit is being powered with. With 5 V on the base, the emitter would be about 4.3 V, and 4.3 mA would flow thru the bottom resistor (Argh, no component designators). That would generate 4.5 V across the top resistor, which clearly isn't possible due to the voltage drops not adding to 5 V.

Let's say the transistor can go down to 200 mV C-E when driven with enough base current. That leaves 4.8 V across the two resistors. Since the transistor has a gain of 20, the emitter current will be 5% more than the collector current. The voltage drops across the two resistors will therefore be equal, which means they are 2.4 V each. That means the collector voltage will be 2.6 V. That's above the 2 V the positive input is fixed at, so the circuit would quickly latch into the first stable state if it ever got to the transistor full on state.

If the base were driven higher anyway, then the B-C junction would be forward biased, and the collector voltage still would not be below 2 V. The opamp output slammed high is therefore not a stable state. This circuit would therefore always end up in the only stable state there is, which is the output slammed low.

So yes, the transistor is always off.

Oops

I just realized that I misread the top resistor as 1.05 kΩ when it is actually 10.5 kΩ. However, that does still not make the second possible stable state stable.

In the second possible stable state, the opamp output is slammed high. This is a ideal opamp, so that means its output will be 5 V (assuming 5 V is also powering the opamp as stated before). With 5 V on the base, the collector of the transistor can't go below about 4.3 V since it would then be forward biased and act as a diode. The negative input would be well above 2 V, so the output would be slammed low and the circuit would latch that way.

Let's see what would happen at exactly the tipping point between the two full-rail outputs. That means the collector is at 2 V, which means 286 µA collector current would flow. The gain of the transistor is 20, so 21/20 of that, which is 300 µA emitter current would flow. That means the emitter is at 300 mV.

That is a theoretically possible state, but not a stable one. Noise always happens. If the collector voltage went just a little higher, the opamp output would go down. That reduces the current thru the transistor, which raises the collector voltage some more, which reduces the transistor current more, ...

So what would happen at this tipping point if the collector current went down a little? The base voltage would go up, causing more collector current, which makes the collector voltage go down, which would make the base voltage go up, etc. Eventually the base voltage would go up enough to forward bias the B-C junction. Now the collector voltage goes up again. When it gets to 2 V, the base voltage stops going up.

Now we actually have negative feedback because the B-C junction acts like a diode. This is therefore a stable state, but not one where there transistor is used in a normal way, or where its datasheet parameters are much guidance.

So now the answer is that there are two possible answers, depending on which state the circuit gets stuck in. In the first, the transistor is always off. In the second, it's B-C junction is forward biased, so it being in "cutoff" or not is no longer a meaningful question.