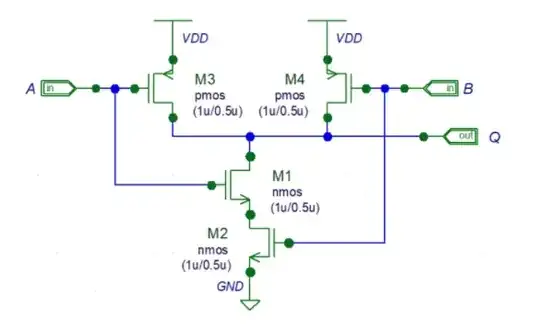

In other words: if we swap A and B, will Q behave exactly the same in DC and transient analysis?

- 119

- 2

- 10

-

7The fact that M2 is ground referenced and M1 isn't might make a tiny difference – BeB00 Mar 05 '18 at 14:35

5 Answers

Depends on the environment.

Maybe in your circuit above and in an FPGA they are the same but in an ASIC library you find differences between the various inputs.

- 14,212

- 2

- 15

- 41

-

I have tried to change the inputs swapping that with each other and I have got exactly the same result that's why I think it is symmetrical. But I can't find good reasoning. – Vahram Voskerchyan Mar 05 '18 at 14:39

-

@VahramVoskerchyan That's faulty logic (ow). Consider this: if I created a NAND that wasn't symmetrical, say had different voltage requirements for one of it's inputs, would it still be a NAND? – candied_orange Mar 05 '18 at 19:18

-

@CandiedOrange But there are asymmetrical logic gates. Pseudo NMOS NAND for example (if I am not mistaken) . – Vahram Voskerchyan Mar 05 '18 at 19:49

-

That's the point. It's faulty logic (ow) to argue that one symmetrical NAND means that all NANDS are symmetrical. – candied_orange Mar 05 '18 at 19:52

-

Both PMOS transistors M3 and M4 will influence the output through their Cgd during switching. However, only the NMOS transistor M1 can do the same. So during switching, M1 and M2 will influence the peaks differently. The needed switching threshold will also be slightly different. The vgs of both transistors are not the same even if A and B have the same voltage. This is because M2 will also need a certain vds to conduct current. – Vahram Voskerchyan Mar 26 '18 at 15:28

There will be a very small difference in that circuit because of the differences in VGS in the N stack while the circuit is sinking current during switching. M1 will be marginally slower than M2 under some conditions.

There are however likely to be other factors, say in how the circuit is laid out, that will have an equally large effect.

Define perfect. Much of what we do in EE is about modelling. The model is never perfect and at most levels of abstraction the behaviour of this circuit would be considered to be symmetrical. If we let very small differences in a circuit that typically would include tens of these gates effect us we will never get anything done.

- 8,418

- 6

- 25

- 40

As the M1 and M2 devices are in a different configuration, there will be a difference between the A and B inputs.

However, you may have to look very hard and carefully to see the timing or threshold effects of that difference.

When you design a logic gate into a system, you work on the maximum specifications, but expect it to behave nearer to typical. There's often a 2:1 or even 3:1 variation between max and typical specs. It's likely that any difference in performance between the A and B inputs will be much much smaller than the difference between the max and typical timings.

- 158,152

- 3

- 173

- 387

-

So we can say that our circuit is symmetrical with some variations ? – Vahram Voskerchyan Mar 05 '18 at 15:41

-

No. In logic terms, it's nominally symmetric. In analogue terms, it's not far from symmetric. – Neil_UK Mar 05 '18 at 15:53

If you care about precision pulse processing, as in building the FlipFlops of a low-jitter PFD, phase-frequency-detector, you should understand all the various ways charges will battle inside the circuit and remain lodged to upset the next pulse, to cause inter-pulse-delay-variations and thus deterministic jitter.

- 33,703

- 2

- 18

- 46

I once made a chip with purposely asymmetric NAND gates, for a ripple-carry adder in which the speed from one input needed to be optimized, and the other not so much.

So no, not necessarily symmetric. But usually very nearly so.