With the base open, \$I_C\$ is close to zero until the device's \$V_{CE}\$ reaches \$BV_{CEO}\$. At that point, \$V_{CE}\$ falls fast and bottoms out, where the lowest \$V_{CE}\$ reached is \$V_{CEO_{SUS}}\$. (Shown on the datasheet as just the maximum spec, \$V_{CEO}\$.)

If a resistor is added from the base to the emitter, then as \$V_{CE}\$ rises, collector leakage current flows and some of this can exit out the base and through this newly added resistor. (It couldn't exit before because there was no path.) Given a sufficient resistor value, then at some point the voltage drop across this resistor will be enough to forward-bias the BJT and then \$V_{CE}\$ rapidly falls, again.

Ultimately, a whole family of curves can be developed and the bottoming out voltage will be different for different values of the added base-emitter resistor. This allows developing a table of how \$V_{CEO}\$ varies based upon the value of this added resistor.

If the base-emitter junction is now reverse-biased, a small depletion region will extend into the base out from the base-emitter junction. And if the collector-base junction is similarly reverse-biased (not uncommonly so), then another depletion region extends also into the base out from the base-collector junction. When and if these two regions join together, "punch through" occurs and the emitter and collector become "nearly shorted." Normally, this is designed against by manufacturers. But it can happen.

Punch through entails secondary breakdown. The main difference between forward and reverse biased secondary breakdown is the level of currents involved (an order of magnitude difference, at least), with reverse biased breakdown often leading to avalanche breakdown (another cause and effect.) For practical applications where these effects may be used, perhaps look at the Gunn Diode. (Also look up the idea of punch-through diodes as a collector clamp.)

There are a host of weird effects. Nature is like that. It's possible that some leakage current can result in internal light being emitted within a BJT at specific sites, absorbed at other sites, and causing a developed voltage that is otherwise difficult to explain. Reality is complex. Simulation is very simple, by comparison.

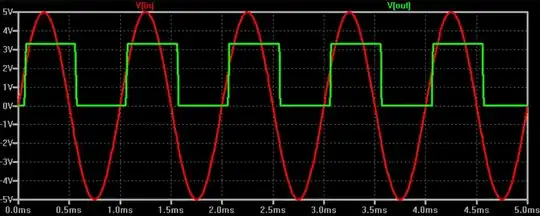

Regarding your displayed values (curves, if you consider a straight line a curve), the simulation models incorporate far more equation elements than I'm willing to display here (because it would take me forever to explain them -- there are entire books on the subject of how simulation handles BJTs.)

But you can very easily make a mental prediction that explains your results. Take the current as \$1\:\text{nA}\$ (not worth trying to narrow it down more than that.) Typical values for \$I_{SAT}\$ for a small signal BJT are in the range of something like \$10-80\:\text{fA}\$. And the emission coefficient is almost always close to 1. So it's very simple:

$$V_{BE}\approx 26\:\text{mV}\cdot\operatorname{ln}\left(\frac{I_C}{I_{SAT}}\right)$$

From this, I get about \$V_{BE}= 26\:\text{mV}\cdot\operatorname{ln}\left(\frac{1\:\text{nA}}{20\:\text{fA}}\right)\approx 280\:\text{mV}\$. No shock there. Pretty close to what your curve shows. It has to be. It's just software doing its thing.