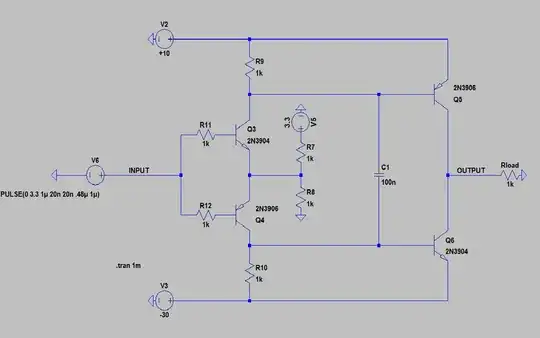

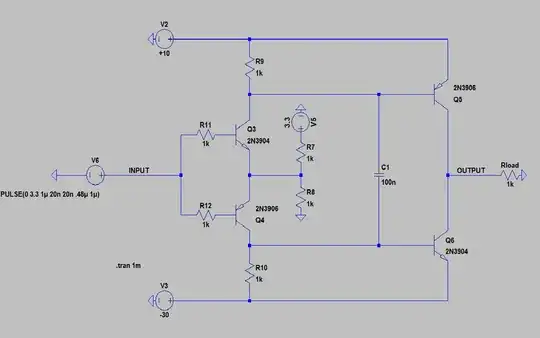

You could make a level translator using discretes. Here is something simple I can suggest (assuming 3.3V logic levels at the input):

LTSpice file

Here are a few explanations: The input is fed to a complementary BJT pair Q3-Q4. The emitters of both of these transistors are biased with a voltage that is set somewhere near the midpoint of the input voltage range (but because it is set using a simple resistor divider, the transistors are actually in a emitter-follower configuration). So, when the input is high, Q3 is conducting, and this makes Q5 turn on. When the input is low, Q4 conducts, and, as a consequence, Q6 does too. So you have a push-pull at the output that is able to swing the required output range. The C1 capacitor is there to help both output transistors switch at the same time, thereforce limiting shoot-through on transistions and reducing wasted power.

The simulation shows it behaves nicely at 1MHz, with ~80ns rise/fall time to swing the whole output voltage range when the input has 20ns rise/fall time, and with a 1k load. The waveform symmetry isn't distorted much, too, so that should be fine for doing PWM. As soon as you add some capacitance at the load, you'll experience problems, though. A few nF is ok, but no more.

Note: this circuit needs significant power, by itself: between 1 and 1.5W, with most power being wasted at Q5 and Q6 (0.5W each, at 1MHz). You could make something more efficient with mosfets, but they are harder to drive correctly at the required timings. The circuit would probably not be this simple (at least the few tries I made didn't show good results).