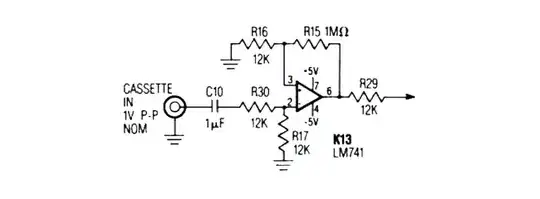

As mentioned in the excellent comment from brhans, the problem is the connection of pin 7 to Gnd (VSS on your schematic). The internal logic diagram for the 4521 IC explains the problem - see diagram below.

Summary: When you drive RESET (pin 2) active (High), the IC tries to make Y1 (OUT1) (pin 7) High - but you have connected pin 7 to Gnd on your PCB.

Therefore you are effectively trying to cause a short-circuit at pin 7 of the IC, limited mainly by the IC's output driver current capability. It is possible that this has already damaged the IC, to a greater or lesser extent. If you are lucky, any internal damage has been confined to the driver for pin 7, which you aren't using. (A different 4521 IC datasheet mentions an absolute maximum output current of 10mA, which you will be exceeding.)

Solution: Fix your schematic & PCB to disconnect the unused output on pin 7. It is normal to leave unused outputs unconnected, not connect them to Gnd. Also, as I mentioned, these ICs might already have been partially damaged, and require replacement if you want to be confident of their future behaviour and reliability.

Again, kudos to brhans for spotting the problem first.

I've edited the original image from the TI datasheet that you linked, to remove extraneous parts. Note that the TI datasheet is a scan of an earlier Harris Semiconductor datasheet, so it does not have the high resolution of typical modern datasheets.

The logic gate just after the RESET signal is an inverter (the remains of other, removed, signal lines make the inverter symbol a little unclear).

In normal use, RESET is Low, IN1 (pin 9) is also Low (as it is connected to Gnd on your PCB). Therefore, after each going through an inverter, the two inputs to the NAND gate in the diagram are both High, and its output is Low. After two more inverters, you see that OUT1 (pin 7) is also driven Low.

Since the logic Low driven on pin 7 is not exactly zero volts, there will be an extra (unplanned) current from pin 7 to Gnd. However, this extra current will be less than in the case below.

This might explain why the ICs are "usually" running at 29°C, on a PCB with a temperature of 21°C.

When RESET is driven High, IN1 is still (fixed) Low. Following the inverter gate on the RESET signal, one input to the NAND gate is now Low. Therefore its output is now High. After those two inverters on the NAND gate output, the IC tries to drive OUT1 (pin 7) High but it cannot do that, due to the (very low resistance) connection of pin 7 to Gnd on the PCB.

That will cause a significant current to flow through the IC and also cause its temperature to rise, as you measured. It may also have damaged one or both of these ICs.

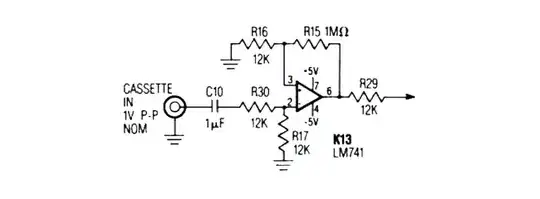

Slightly clearer internal logic diagrams of the 4521 IC are available in the datasheets from:

They show the same gate structure between the RESET, IN1 and OUT1 pins as in the (poorer resolution) TI datasheet, and so they will behave in the same way, when the RESET signal is High (active).