I'm really discouraged with MOSFET amplifier biasing.

The results of my experiements my be found here: MOSFET amplifier mid-point bias

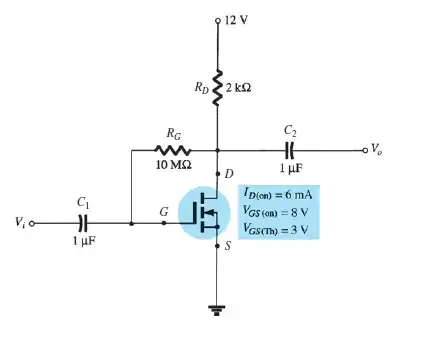

Voltage-divider schematic:

I found that for voltage divider biasing I can set Q-point with some approximation. I can't calculate divider to make V_drain to be half of the amplifier voltage source VDD0. It need to tune schematic with additional resistors.

Can anyone show any recipies of MOSFET amplifier biasing with equations or links to another posts for example?

I also may not fully understand what is Id_on? Some books say that it's a current at which MOSFET first move into saturaion region but another tell that at that value the MOSFET go into fully on mode (as switch). What is it in reality?

Also I found that for voltage divider bias there is overdrive voltage eixts Vovd = Vgs - Vth and Vds > Vovd, why it's so and how to view that on graph?

A'm also interested in how really bias point set in the next schematic. I think that in this schematic Rd resistor determines the limits of Id current. And the actual Id current can't be properly setup. Is it so?