For general purpose PCBs that consist of an MCU (simple 8-bit, 20MHz), switching vreg (1.5MHz), and perhaps some SPI and I2C clients (such as sensors, wifi, gps modules, etc), what are recommended and typical baseline capacitors recommended to place near the power supply pins of each component?

I realize some ICs provide some recommendation on their datasheets, but many of them don't.

Assume, that the maximum inter-IC frequency is on the order of MHz (perhaps 1-4MHz at the most). Although it also matters that the actual transistor switching frequency inside these chips is equally (perhaps more) important.

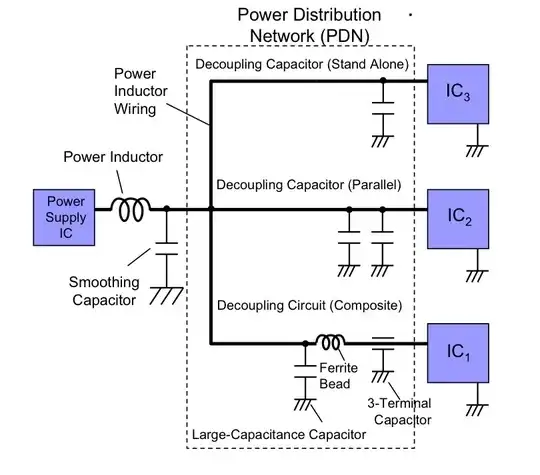

I've seen references of adding a few capacitors at each IC, differing by "decade capacitance". In the past, I've typically just used 10uF in parallel with 0.1uF, MLCC capacitors, which seems to have worked. However, I'd like to know if there are other recommendations. How about adding a 1uF or a 0.001uF in parallel as well?

I suppose the answer to this question depends on trace length, possible noise sources, IC characeristics, etc...but assume general/typical/average case.