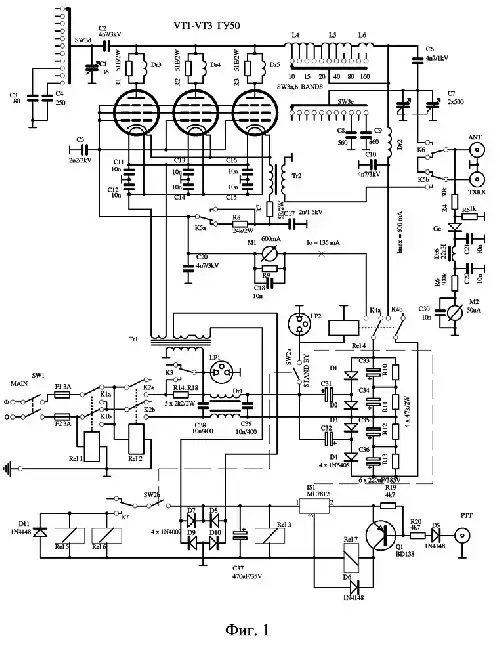

I was experimenting with a simple voltage level shifter to convert a signal from 5v to 3.3v.

Then i went to simulate my circuit in orcad pspice, and i need help understanding what is causing the voltage spikes. I'm using a pulse generator to pulse a 1kHz signal in to the gate.

Is it the rise and fall times of the pulses that is causing the spikes?