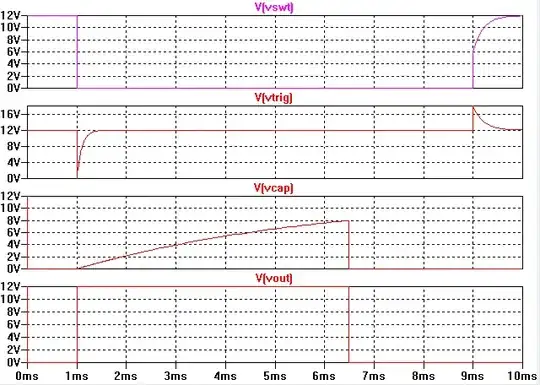

I recently wired up a 555 timer in a mono stable configuration and found that when the trigger was held low for longer than the configured output pulse width, the output would stay high. After thinking about this.. it made sense. My 555 timer is wired like so:

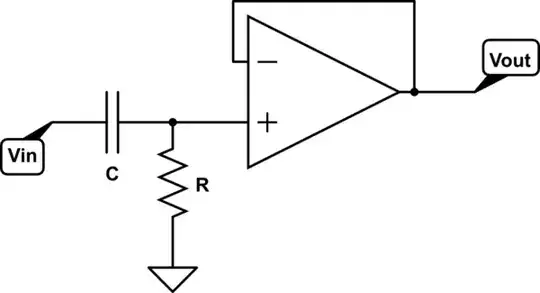

I searched around on the web and found an article. It explains that including a capacitor on the input causes a very brief drop on the input when the input signal goes low. Even if the input signal says low, the input to the 555 timer goes high immediately after triggering the 555 timer. The 555 timer won't give a high output until the input signal goes high, then low again to trigger another output pulse. The part of the input they suggest is wired like this, which is what i'm most curious about.

Why doesn't the capacitor keep a direct path to ground? I know capacitors don't really allow DC current to flow, but what allows it to discharge to ground at all?

Even more tricky, why does it also work properly with a capacitor in series with the input and one end floating (open switch)?

This cap on the input is really confusing me.