I want to use a STM32 microcontroller to read data from a multi-channel ADC. The microcontroller that I intend to use will most likely be something from the F7 series (such as STM32F746ZGT), whereas the ADC that I currently have my eye on is LTC2358-18 from Analog Devices.

The project that I'm working on requires me to simultaneously read 6 analog channels (with a reasonable data rate). As far as I understand, the particular ADC chip can output its conversion results on different serial data output (SDO) channels that can be read out in parallel (the serial clock is identical for all of them):

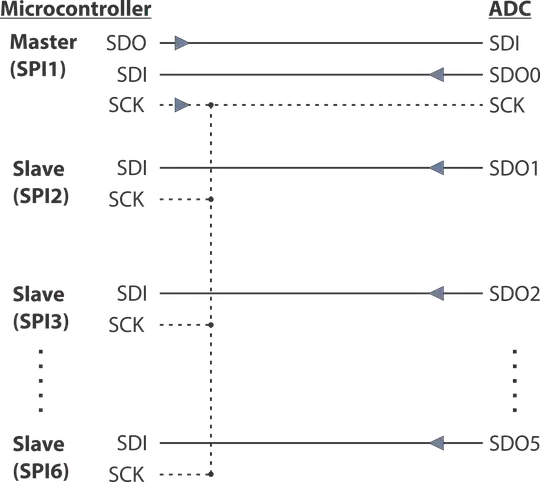

I was wondering if it is possible to use a single STM32 MCU to read the 6 channel output data via SPI (I don't really need the two remaining channels). In general, I would assume that I need to configure 6 SPI interfaces that are available on STM32F746ZGT, as follows:

- One of the SPIs acts as the master and provides the serial clock (SCK) for all the slave devices (5 remaining SPIs on the STM32 chip and the ADC) and the serial data out (SDO) for the ADC configuration. The master would (I'm guessing) pull down the CS for all the SPI slaves.

- The remaining 5 SPIs on the STM32F746ZGT share a common SCK line and each are linked to a SDO channel on the ADC.

Or, in other words, it would look something like this:

Would this kind of configuration actually work or am I missing something?