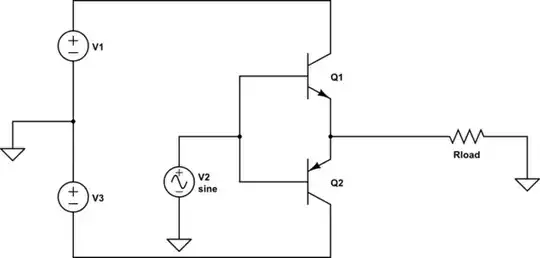

I am confused as to how the following circuit will work(????)

Lets assume that there is no AC signal and only a DC signal is applied.

According to the books this is a voltage follower stage i.e Vo will be equal to Vi. But how is that possible? Both the transistors are always in cut off because Vgs of NMOS and PMOS should be zero and hence Vo should be floating. But if I sweep Vi from 0 to Vdd then I also see Vo following Vi. How is the output voltage Vo so well defined?

Intuitively this circuit makes no sense to me at all. It would be really nice if someone could explain me in simple words!

EDIT: I will try to explain what i think should happen. For the circuit exactly as described in the picture (no load condition and only DC condition)

When Vi is open or gate terminals are floating, with Vdd applied, Vo is floating.

When the gate terminals are connected to Vi, and Vi = 0 volts, Vo is still floating (considering Vo_floating > 0 volts is most likely, than Vo = 0 volts), VgsPMOS = negative voltage, hence PMOS will pull Vo to ground. 2.1: If Vo_floating = exactly 0 Volts (Vo=Vi) then it is the same case as 2.

When Vi > 0 but less than Vth(PMOS and NMOS) VgsNMOS = +ve and VgsPMOS = -ve (since Vo >=0), Vo = 0 volts

Vi > Vth but Vi << Vdd imples, VgsNMOS > VthNMOS and -VgsPMOS < -VthPMOS, hence both the transistors are conducting. VgsNMOS = Vi-Vo, hence Vo=Vi-VgsNMOS. However at this stage Vo = IdRdsPMOS, where Id is the drain current that will be defined by VgsNMOS (Id = gmVgsNMOS).If RdsPMOS is very high then Vo will increase reducing VgsNMOS. But what if VgsNMOS drop below Vth? Why cant this happen? What will define Vo (is it Vo=Vi-VgsNMOS? or Vo = Id*RdsPMOS?) here and why?