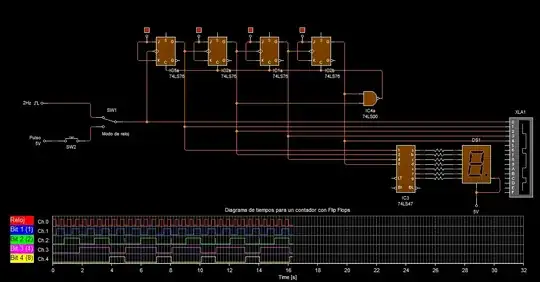

I am trying to simulate a decade counter using a ripple counter 4 bits and a NAND gate to reset the 4 J-K flip-flops when it reaches 10 (1010).

The thing is it does not reset but goes to 4 (0100) due to the reset on my second flip-flop (it sends a negative edge to the next one plotted on pink) as shown in the plot (the tiny line on the green plot). is this a failure on the simulation or in the design? Any suggestion to solve that will be appreciated