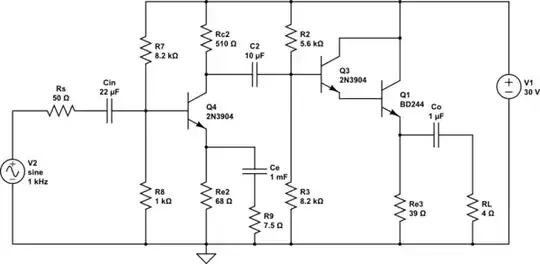

Here is shown the design of simple multi-staged amplifier.

simulate this circuit – Schematic created using CircuitLab

I tried to put together all three NPN transistor configurations and this is what I got - just redrawn schematic of each individual configuration connected together.

First I was hoping for optimal power transition between stages and that was meant to be achieved by proper impedance matching between the output and input of each individual stage. Then I tried to achieve desired voltage gain of each stage (with formulas shown later). When I was calculating voltage gain of each stage individually I did consider the ohmic resistance of next stage that was "loading" the first stage (or the stage for which voltage gain was to be calculated).

I set the amplitude of function generator on the value of only 10mVpp, so the output voltage wouldn't be clipped at the first place. The power supply DC voltage was high enough too, so the clipping could be avoided. Maybe you will be wondering why are values of last stage voltage divider so low (which is not usual for a voltage divider) - as I have said, certain input/output impedance formulas needed to be matched for optimal power transition + 14.4V drop across R1''' and 15.6V drop across R2''' (which is also not usual for voltage divider).

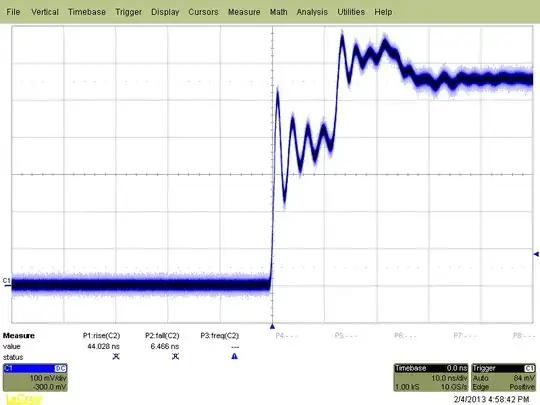

- Circuit was observed by oscilloscope (analog) and the resulting amplitude of loaded amplifier was a disaster - output was greatly distorted; not clipped but distorted in many different ways. So my question is: Where did I went wrong on this one?

I should also note that calculated loaded voltage gain calculus of each individual stage had very unrealistic values - voltage gain of whole circuit was somewhere about 80k...

This was also my first multi-staged amplifier ever made, so I must admit I was very disappointed upon the results.

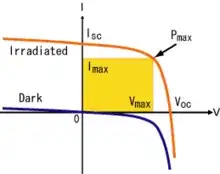

Here are listed formulas used in this "amplifier" design process: