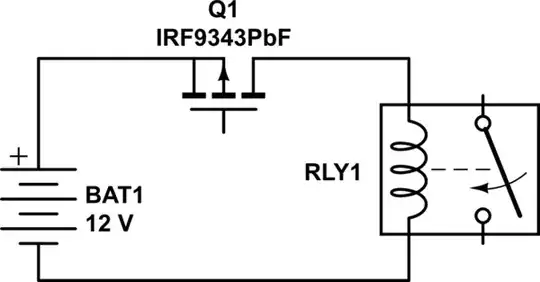

I'm using the P-channel half of an IRF7343PbF as a high-side switch to actuate the coil of a Gigavac P115 relay. I would like to be able to turn off the relay as quickly as possible after detecting an overcurrent fault downstream, in order to break the high-power circuit before the fuses blow.

simulate this circuit – Schematic created using CircuitLab

If I use a freewheeling diode across the relay coil as is typical to protect transistors switching inductive loads, the contacts take almost 20 ms to open - too slow. With no diode, at turn-off the transistor avalanches with about -60V across Vds. This lets the relay coil current fall much more quickly and the contacts open only 3 ms after the gate is commanded high. I measured the Id and Vds waveforms and the integral of their product gives an avalanche energy around 1.6 mJ. This is in between the MOSFET's single-pulse avalanche energy rating (114 mJ) and its repetitive avalanche energy rating (0.2 mJ).

So what do they mean by "single-pulse"? Is it really only permitted once in the life of the device, or can you do it as often as you like provided Tj is at room temperature before each pulse? In my application the avalanche would occur a few thousand times over the life of the system, and never more frequently than about once a minute. The junction temperature should stay cool. Am I risking cumulative damage to the FET by repeatedly (if infrequently) forcing it into avalanche?

FWIW I gave it 500 cycles on the bench at 1 Hz and it seems to be fine so far. That doesn't mean I'm not abusing it though.

Of course I can avoid this issue by using a bidirectional TVS across the coil with a clamping voltage around 50V, but I'd still like to know.