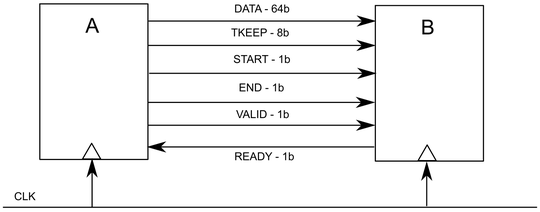

I have following design and need to insert pipeline stage between components A and B (design doesn't meet timing constraints in Quartus II due to long data path between them)..

Simple register won't do since interface (basically simplified AMBA AXI4-Stream with START of frame signalization) between them is handshaked (B sets READY signal when it completes work on data and is ready to receive another). Work usually happens in one clock tick (so READY is almost always high) but it doesn't have to be and I need general solution to use throughout my design.

What do you (or industry) use in these cases? I don't really want to reinvent the wheel :)