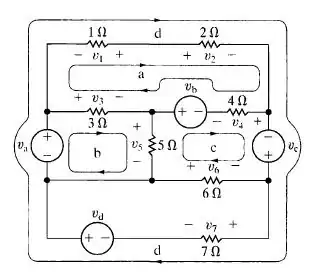

I have been trying to build a simple VGA using an op-amp and JFET for gain control. I get good results over a small range of voltages (like factor of 10) but as soon as I try to improve this, the signal gets distorted in on or another way. I figured using multiple variable gain stages would be quite bad because the Drain-Source Voltage of the FET needs to stay as low as possible for good linearity. That's why I thought it would be best to make a single variable attenuation stage and then amplify after that. The attenuator looks like this in SPICE:

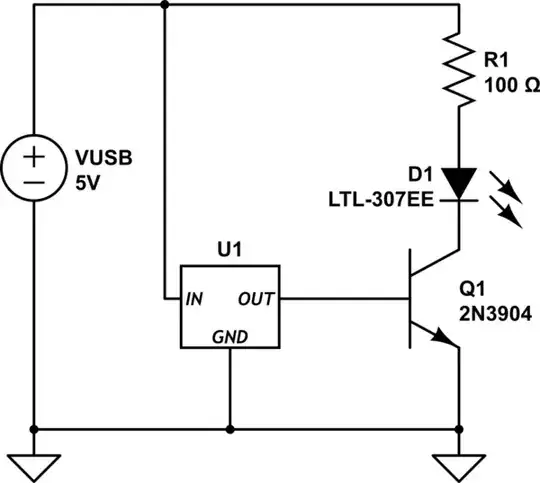

Unfortunately, I always get this pattern of distortion (both in SPICE and on a breadboard) when I'm attenuating by a lot (\$V_{GS} < -2V\$ in this example):

The negative half of the output sine (positive half of the input sine because it's inverting) gets flattened out for some reason. I'm trying to fully understand why this is happening. I thought it might be because

$$V_{DS,SAT} = V_{GS} - V_P$$

and the positive half gets into the saturation region but this doesn't seem to be the case because \$V_{GS}\$ (blue trace) rises by more than the amplitude of the sine wave without it changing the distortion:

I hope someone can explain why this is happening.