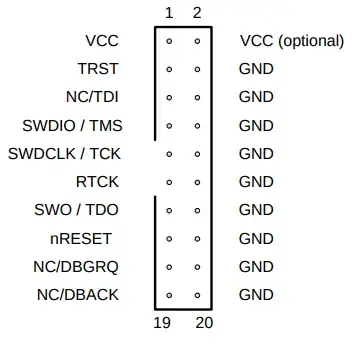

There is a big confusion in my head about debug connectors for ARM microprocessors. If I just take a look at this documentation there are a couple of JTAG connectors mentioned:

- Cortex 10-pin JTAG/SWD (usualy 0.05" pitch) which supports JTAG debug, SW debug, SW viewer

- Cortex 20-pin JTAG/SWD/ETM (usualy 0.05" pitch) supports JTAG debug, SW debug, SW viewer, trace operations.

- Traditional 20-pin JTAG/SWD (usualy 0.10" pitch) supports JTAG debug, SW debug

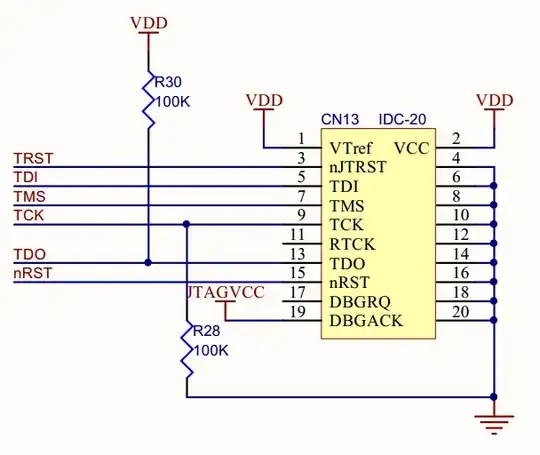

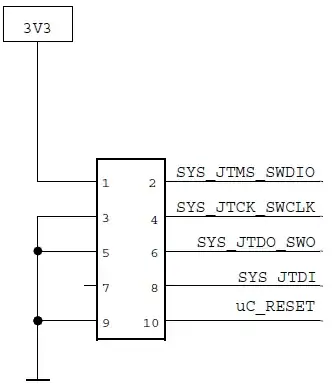

Now I could only find schematic on how to connect the Traditional 20-pin JTAG/SWD to the microcontroller and it is this one:

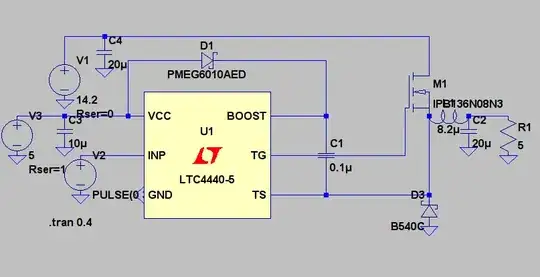

To completely understand the schematic I will paste power section as well. This is important, because it looks like entire circuit is powered by JTAG pin 19 which is connected to power regulator and then goes back to the JTAG connector pins 1, 2, 13...

Does anyone have any schematics for the other two?