I'm trying to build a boost converter with current mode PWM control, but I'm stuck at selecting capacitor and resistor values for compensation. I'm using a LT1619 as the controller IC:

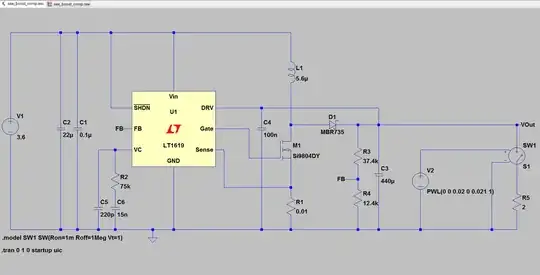

simulate this circuit – Schematic created using CircuitLab

Datasheet: LT1619

Boost converter parameters:

\$V_{in(min)}=2.7 V\$

\$V_{in(max)}=3.6 V\$

\$V_{out}=5 V\$

\$I_{out(min)}=0.5A\$

\$I_{out(max)}=1 A\$

\$f(switching)=31250Hz\$

\$\Delta I(step-min)=50mA\$

\$\Delta I(step-max)=200mA\$

\$Overshoot\;step\;load\;error:100mA\$

\$V_{dc(error-tolerance)}=10\%\$

\$V_{out(ripple)}=90mV\$

\$V_{noise(max)}=50mVpp\$

\$Minimum\;phase\;margin\;at\;a\;again\;of\;unity: 8\%(from\;overshoot)\$

\$Operating\;temperature\;range:-30\;degrees\;celsius...+120\;degrees\;celsius\$

\$Capacitor\;tolerance: 10\%\$

\$Inductor\;tolerance: 5\%\$

The problem is that I do not know how to calculate the capacitor and resistor values. I know that the feedback network is a complex aspect and it's not easy to understand, but I believe that if someone explains this to me from 0 to top (a thing which online sources apparently fail to do) then I can comprehend it.

But, I don't know, there might be too much to explain. I would appreciate if someone could provide a basic explanation and then point me to a document from where I can learn if that's the case.

I think this is all the needed information, but if more is necessary, then I'll be ready to post it.