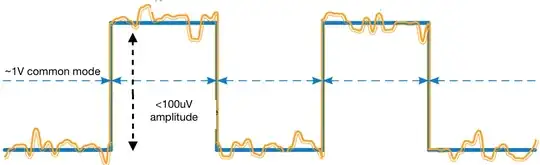

Common mode changes slowly, signal changes fast.

What you thus need is a high-pass filter, which filters out the DC component. In the easiest case: that's a capacitor in series with your signal source, with a resistor to ground to "short" low frequency content. here's an easy-to-use RC high-pass design tool. Start with something like C=10nF. You seem to be very concerned with preserving voltages: that's the job of designing a proper filter, and this tool helps. You'll need to figure out the signal of interest's frequencies first!

You'd get a spike at the high-pass filter output for every one of your "blue" signal's edges (because that edge is a very fast changing signal).

After the high-pass filter, you only get your signal of interest centered around whatever bias you use (hint: you resistor from the filter can also be split into a voltage divider between supply voltage and ground, so that you can bias your signal into the center of your amplifier's operating range). Then, you just amplify that, so that the signal of interest spans as much as possible of your ADC range.

The spike that you'll get when the high pass filter sees your clock's edge is not that bad, filter it out digitally. (you'll not lose many samples to that spike's "overamplification") Especially if you know the period of the blue signal, digitally filtering it gets very easy.

Don't forget:

You're using an ADC. You hence must also have a low pass filter that limits the bandwidth that reaches your ADC to half your sampling rate! Otherwise, you'd get aliasing, and your signal will be unusable.