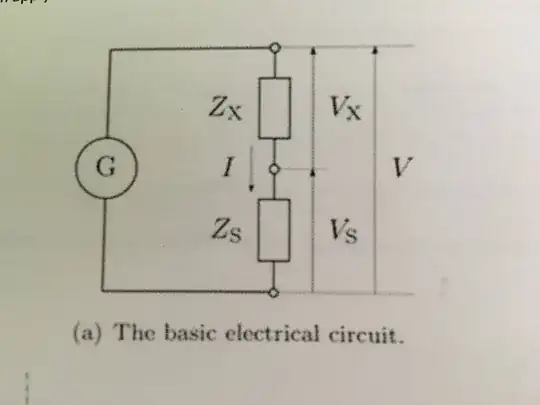

I have made a Sample & Hold circuit using Multisim but after simulating oscilloscope showing sampled version of input waveform for positive half cycles only. I have used MOSFET as a switch with controlled voltage and its working fine.

I have made a Sample & Hold circuit using Multisim but after simulating oscilloscope showing sampled version of input waveform for positive half cycles only. I have used MOSFET as a switch with controlled voltage and its working fine.

My question is why I am not getting sampling of negative half cycle even though MOSFET is open circuited?