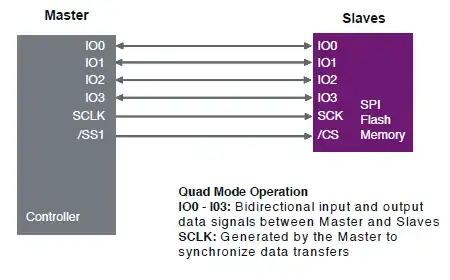

Reading an SPI Flash datasheet, I encountered the concepts of "dual I/O" and "quad I/O". At first I thought that "dual I/O" was synonymous to "full duplex", but then what is "quad I/O"?

What is dual I/O and quad I/O, and how do they compare do duplex and full duplex?