A few more:

I really hate having to deal with other people’s work that’s drawn on half-grid. It’s a huge waste of time and doesn’t add any value to the drawing.

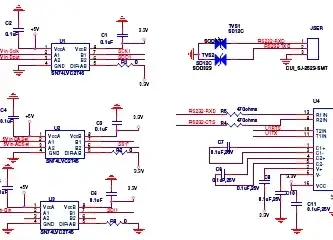

- (2) Use ‘physical’ style for smaller devices.

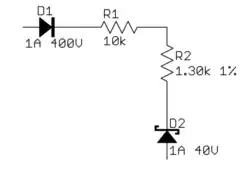

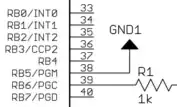

Drawing ICs and small components with the pins in order helps with conveying your intent to layout, and makes debugging much easier. This goes double for transistors and diodes in sot-23: I draw them showing the pin order, and as a result haven’t had to rework a mis-laid-out one in years.

- (3) Realize the limits of (2) above.

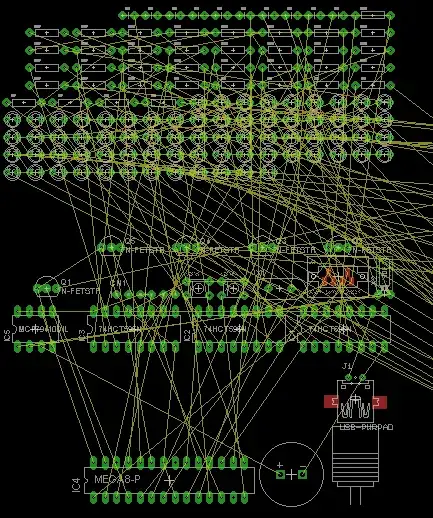

It’s not possible to draw a big BGA physically, or even as one symbol. But you can at least separate by function and show how pins relate to each other spatially. For example, an FPGA can be drawn and divided to show blocks that represent logic tiles, and the tiles themselves placed / ordered on the schematic to show how they route out.

Historically, multipart symbols for elements like op-amps or gates made sense. But these are becoming more rare in designs.

- (4) Intra-page named aliases are ok, but don’t push it.

Named aliases are the same as off-pages really: it means you still have to scan the page to look for its other instances. With a PDF schematic and Ctrl-F this isn’t as big a chore as it used to be (and shame on you manufacturers who make non-searchable PDFs. That’s just lame.) That said, off-pages are more rigorously checked by DRC than aliases.

- (5) Block diagrams and mechanical plans are worth the effort

The effort you spend conveying your thinking here will save lots of time over the life of your design - from layout to repair. Yes, your mechanical designer will make the ‘official’ board outline, but at the very least you can convey where you expect stuff to be placed - and why - by doing these two kinds of diagrams.

- (6) When you export your schematic to PDF, make it searchable.

Is it really too much to ask?

- (7) Have just enough component information.

Besides the reference designator, some designers are tempted to have all the part attributes on the schematic. But do you really need them? No, you don’t. Tolerance, sometimes. Voltage, sometimes, when you have a section that’s at a higher voltage. Footprint - maybe. Manufacturer part number? Rarely - you’d want to multiple source usually. Corporate AVL/MRP number? Nope, never.

All this other stuff is what a BOM is for.

- (7a) Think ahead to BOM generation.

That said, developing some kind of part number system even in your early days allows you to create detailed BOMs even if you don’t have an MRP system. Each part type should have a unique ID that is set as a hidden attribute in your schematic that corresponds to an entry in your master parts list (AVL list.) You use that ID later to merge in the expanded info from your AVL list to create the detailed BOM.

Even later, you can import this stuff into a real MRP or PLM system such as Oracle Agile.

- (8) Power is a signal, too!

It used to be that you’d draw a schematic with ‘hidden’ power / ground pins which would be automatically aliased to VCC or GND. It’s still an option when you create a symbol in Orcad for example. Don’t hide those power connections! Show ‘em! Especially considering today’s designs with multiple power domains, high power density, routing, bypassing, loop area, and so forth.

Power is so important, that if you’re not spending at least 1/3 of your time on power design you should consider another line of work.

- (9) Comments are your friend.

Highlighting key elements with text can save a lot of time in debugging. I will typically comment things that relate to software (e.g., addresses, bit locations) and power design (current typical/max, voltage).

Use 11x8.5 (A size) for really simple stuff, 17x11 (B size) for most other things. Go larger only if you really need to.

17x11 (or its nearest metric equivalent) is a reasonable size for viewing on an HD screen or for printing even at 11x8.5. It’s a good go-to size to work with.

On the other hand I find that I can’t get enough stuff on 11x8.5. And on the other, other hand is the other extreme when I’ve used 23.5 x 15.2 (scaled-up B, not C) for a really complex drawing that groups together (e.g., DRAM banks): this needs to be printed at 17x11 to be reasonably easy to read in hard copy.

As it is I rarely print anything anymore, so worrying about how hard copy comes out is more trouble than it’s worth most of the time.

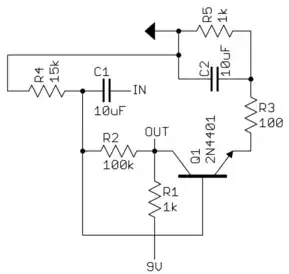

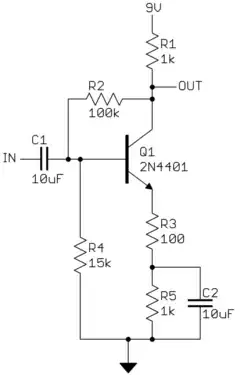

- (11) Left-right signal flow, top-to-bottom power flow. Mostly.

This is the general standard to make understanding the relationships of elements easier. But sometimes giving more more weight to architecture flow than this old rule yields a clearer schematic.

- (12) Organize off-pages / ports in vertical groups.

It’s not necessary or useful to drag ports to the edges of the schematic. But at least line them up in organized columns so that they’re easy to scan visually.