I'm developing a four layer board which is powered by 3 voltages - 1.8V, 3.3V and 5.0V. The board has the following stackup:

- Signals

- Ground

- 3.3V

- Signals

The ground and 3.3V plane are completely unbroken. No signal or power trace travels on them.

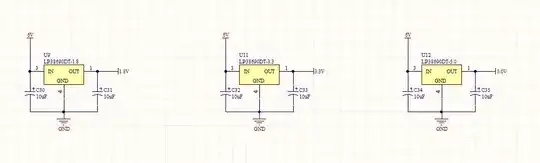

I'm using three LP38690DT LDOs to provide power - here's my circuit.

Click here for larger picture.

My concern is the layout for these devices. The datasheet suggests the following

The best way to do this is to lay out CIN and COUT near the device with short traces to the VIN, VOUT, and ground pins. The regulator ground pin should be connected to the external circuit >ground so that the regulator and its capacitors have a "single point ground".

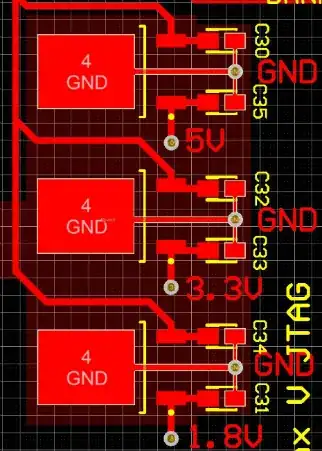

I was somewhat confused by the term "single point ground" but I tried to follow the advice given in the datasheet to the best of my ability - but I am not sure if I am correct:

Note that the text in red is only there to give clarity to the folks here - I will delete it afterwards. Each regulator is connected directly to the capacitors and the ground pin of the regulator is connected directly to the capacitor's ground pin directly. Is this what the datasheet meant I should do?

The datasheet goes on to say

Since high current flows through the traces going into VIN and coming from VOUT, Kelvin connect the capacitor leads to >these pins so there is no voltage drop in series with the input and output capacitors.

What does it mean by Kelvin connect? I know what a Kelvin Connection is - what I don't understand is what does it mean in context for a LDO.

My third question is regarding all three regulators. As I mentioned, each IC is referencing ground from the same via that connects it's capacitors to the ground plane. However, should I connect all three regulators to the same ground point i.e. should all 3 regulators connect to the "single ground point/via"?

Finally, the input voltage is being fed by a 4-point through hole connector which carries 6V on two conductors and GND on the other two. The GND pins are connected direcly to the ground plane. Is this OK or should I connect the GND pins to the GND pins of the regulators directly via thick traces?

NOTE: the layout picture does not show anything connected to the output of the regulators. This is OK. I still have to connect my ICs to the power. ALSO: the maroon color underneath the regulators is not a net. This is Altium's way to show "Rooms" in PCB layout.

CURRENT REQUIREMENTS

Most of the current is drawn from the 5V supply. The 5V supply connects to a LCD display which will draw a max. of 400mA (when backlight is on) - but normally around 250mA.

The 3.3V supply will draw a max. of 300mA (discontinuous) but normally around 150mA or less.

The 1.8V is the supply for the core of the CPLDs that my board has. I was unable to estimate this but I've measured it. At startup, this was around 30mA but then reduced to 0mA. My meter, it seems, was not sensitive enough to actually measure the current. I reckon 200mA would be a safe bet for this.

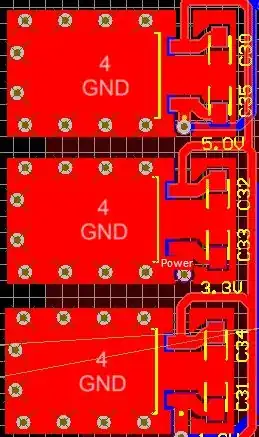

UPDATED LAYOUT:

I hope this is what folks here meant. I wasn't sure if I should one large copper pour or three separate ones so I went with 3 separate ones.

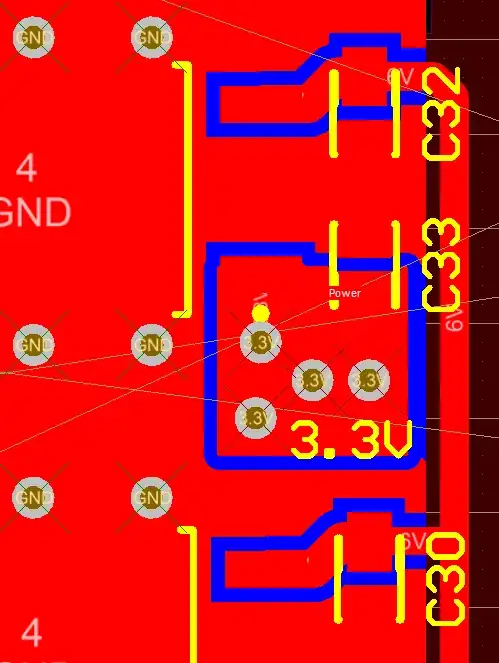

UPDATED LAYOUT (again):

I've now made made one giant copper pour instead of 3 independent ones. I was't sure how to connect my 3.3V voltage to my power plane using multiple vias so the above is my attempt. I made a small fill and connected it directly to my output capacitor. From there I have 4 vias, each 25 mill in size, connecting directly to my power plane. Is this a better way to do it?

The clearance between the fills and other objects is about 15 mills. Should I increase this?