While trying to configure the GPIOs using CMSIS on a NUCLEO-F103RB board, I couldn't seem to find in the reference manual how one is supposed to choose between internal pull-up and pull-down resistors.

Page 160 shows the configuration of the CNF and MODE bits and shows that the bits are the same for pull-up and pull-down. Searching the entire PDF file for "pull-up" and "pull-down" yields no results. The errata also has no mention of this.

Did ST seriously forget to put this information in the manual? If so, how come no one has noticed this? Or am I just being blind?

Anyway, looking at their standard peripheral library, it seems that writing a 1 to the corresponding bit in the GPIO BRR register activates the pull-down resistor, while writing a 1 to the BSRR actives the pull-up resistor:

/* Reset the corresponding ODR bit */

if (GPIO_InitStruct->GPIO_Mode == GPIO_Mode_IPD)

{

GPIOx->BRR = (((uint32_t)0x01) << pinpos);

}

else

{

/* Set the corresponding ODR bit */

if (GPIO_InitStruct->GPIO_Mode == GPIO_Mode_IPU)

{

GPIOx->BSRR = (((uint32_t)0x01) << pinpos);

}

}

This code can be found in the stm32f10x_gpio.c file.

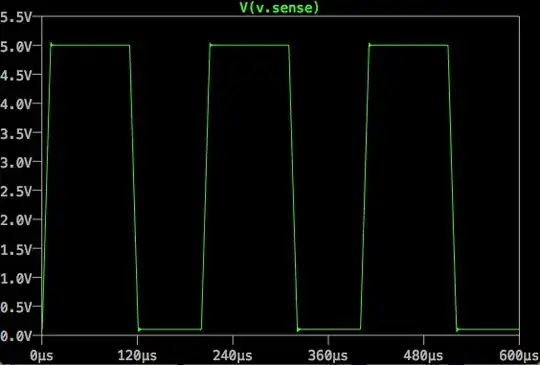

![[![enter image description here][1]][1]

[1]: https://i.stack.imgur.com/CwAT3.png](../../images/3810724965.webp)