I'm wondering people's thoughts on what happens when SPI timings between master and slave are "a bit" off. A bit being 2.34375 % too slow.

My setup is:

- Slave device, which I cannot change, wants to be fed a clock of 128000.

- My master device, which I can change, is currently stuck at 125000 due to the crystal that I have in it, 8 MHz.

I have ordered an 8.192 MHz crystal from RS with capacitors which will arrive in a few days. When that is running my master device, they will be in bitrate harmony.

In the meantime, when I read from the slave, it is returning data but it's a bit of a mess. I don't know if it's my bitrate mismatch or some other comms issue that I've not yet got under control.

What do you think? * Never going to work until bps are matched? * Should get some data coming in correctly but after N bits it'll start going wrong.

I know the latter can apply to UART but I'm unsure of SPI. Of course, in UART there is no shared clock, and in my setup, I'm providing a clock that is 2.34375 % too slow.

Thanks for your thoughts.

Rich

Added: the kit I'm talking to is circa 15 years old. It wont be some modern 32 bit ARM cored thing, it's a car CD player from the turn of the millenium.

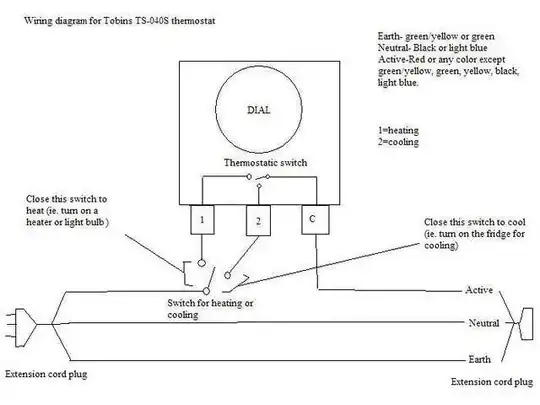

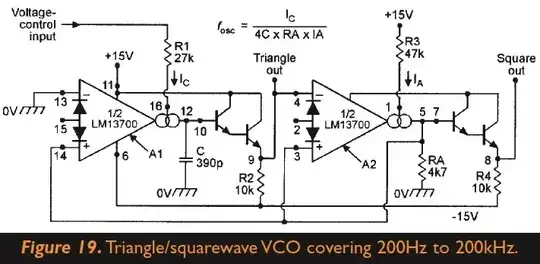

Pictures that show 'good' and 'bad' behaviours:

This is the proper behaviour, between my CD player and geniune connected equipment:

This is with my incorrect clock rate:

This makes me wonder if the slave device is infact a real SPI device, or some microcontroller doing bit-banging out of time to me.