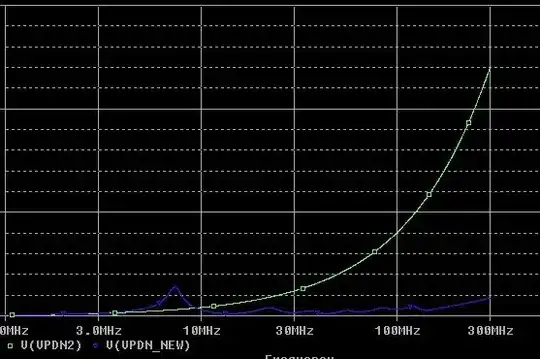

We are using DC-DC switching regulators on board (switching freq. of regulators are ~540KHz). There is periodic noise in power/gnd at 540Khz. If we change the switching freq. of regulator, the periodic noise changes accordingly.

We observe there is issue with LVDS signal (125Mhz) w.r.t to this switching noise of regulator. Attached are screen shots of my board cicruit (125Mhz OSC and LVDS buffer) and scope measurement. The LVDS signal is captured at buffer input. This is a multi-layer board with adequate layer/return path on board.

In my other designs, there exists DC-DC switching noise, but there is no distortion of LVDS signals.

How do I find where the distortion is coming from?