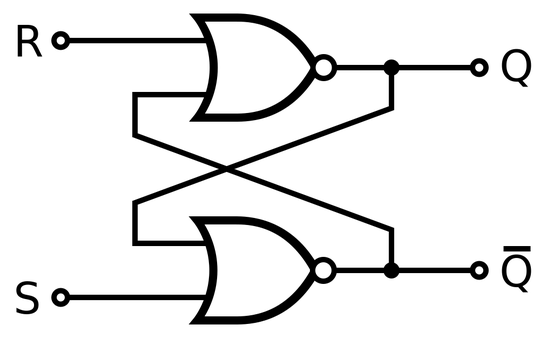

I am studying Computer Science and I am very confused. Let us say our Q is 1 and our Q* (Negation of Q) is 0. So when we go for R = 1 and S = 0, why isn't the value of Q* = 0?

I mean the NOR Gate for Q gives us Q = 0, which makes sense for me. But why is this value taken for the input of the NOR Gate for Q* instead of the earlier saved one (which was our 1). How is it accomplished? Shouldn't be the NOR Gate for Q as fast as the NOR Gate for Q*?