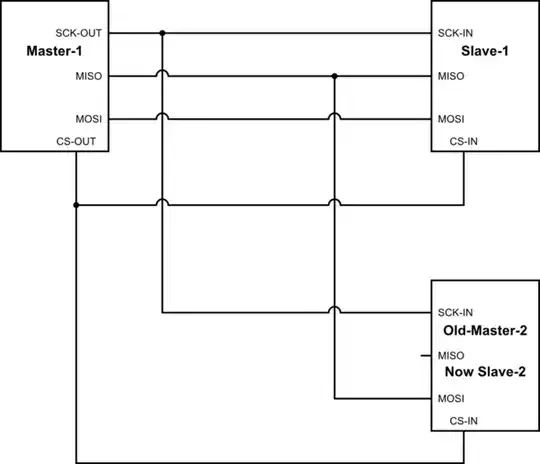

I am using two STM8 micro-controllers as SPI masters. Master-1 is configured in full duplex mode. And the Master-2 is configured in Receive-only mode. The CS, MISO, MOSI and SCLK lines of Master-1 are connected to the Slave. The CS, MISO and SCLK lines of Master-2 are connected to the Slave. When Master-1 requests data from the slave. Master-1 and Master-2 should receive the data from slave at the same time. And the data should be same. I configured two masters with same baudrate,CPOL and CPHA.

When I am communicating with single master, I could receive the data correctly from the slave. But When I involve the second master in the communication the received data of both master is corrupted. And in the oscilloscope, I could see the SCLK variations on the slave.

What are the things I need to consider while communicating a slave with two masters at the same time.