I've been building a project using some Infineon IPA093N06N3 MOSFETs. I carefully picked the correct values for the MOSFET that I needed, and calculated an estimated Tj based on the thermal resistance of the package I was using.

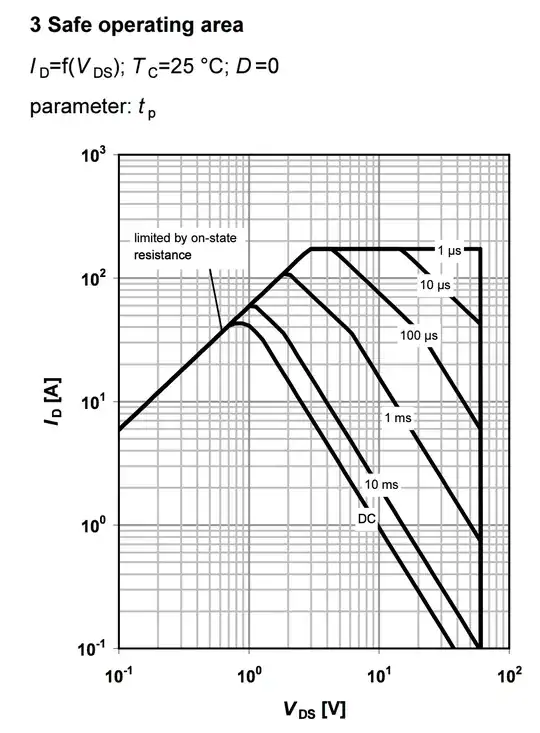

I only just noticed today the Safe Operating Area graph in the datasheet whilst looking up the pinout for the package. The SOA suggests that this MOSFET (and a lot of others I took a look at afterward) is only rated to "safely operate" in a very small window, despite the much larger maximum operating conditions listed on the first few pages of the datasheet.

Taking the linked datasheet above as an example, it states that the MOSFET is capable of a VDS of 60V and a ID of 43A. A further look on page 4 shows the SOA graph, which states that at any VDS over 10V you are limited to a ID of 10A. I previously assumed that, so long as you stayed inside the maximum ratings and you could cool the MOSFET to below Tj(max), that any value for both of these would be alright.

If the MOSFET is capable of switching a large current whilst staying under the Tj(max), what other limiting factors might there be that would cause the manufacturer to state that they are only capable of smaller currents above certain voltages?