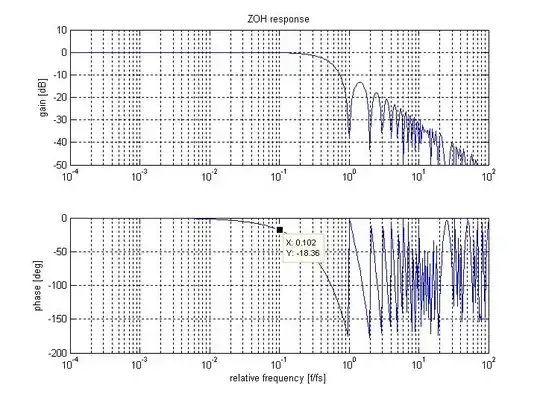

I would like to simulate a simple one-bit counter (or frequency divider) using the D-flip flop.

However, I don't want to use the abstracted D-flip flop above. Rather, I want to simulate this using primitive NOR/AND gates directly. I rigged up a D-flip flop based on NOR Gates below.

The full simulation can be seen at this link: http://tinyurl.com/z6mae9c

However, I cannot connect the Q' output back into the "D" input without getting an error (endpoints circled in red below). Can anyone recommend how to fix this? Is this a limitation of the simulation framework? If so, what's a good package to simulate this on?