Unfortunately there's no simple answer to your question. There's too many variables in the problem for anyone to have measured or characterized every possible configuration: thickness of the FR4, number of copper plane layers, number of vias between the plane layers, the amount of air flow over the board and the inlet air temperature, the thermal contribution of other nearby parts, etc., etc.

There are standard test methods, but these are hardly relevant to any real situation, mainly because they use just bare FR4 with no copper layers as the heat spreading element. Various vendors have also published values for certain configurations. The datasheet you linked, for example, refers to IRF's AN-994, where they give thermal resistance values for various packages offered by that company. But note that their standard test condition uses 2 oz. copper on the outer layers.

Linear technology is another company that publishes informative thermal results. If you can find one of their parts in the same package as your FET, and check the datasheet, they'll likely give a table of thermal resistance for various sized heat spreaders on the top and bottom layers.

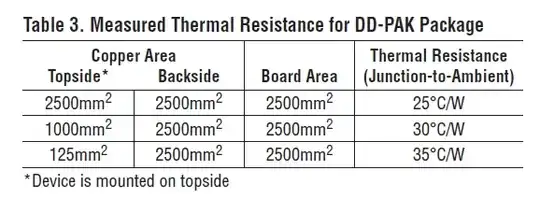

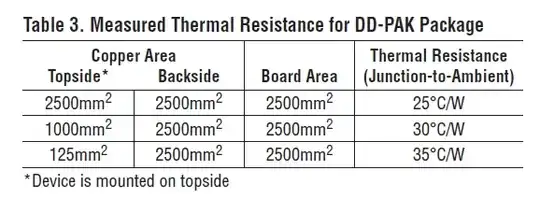

For example, for their DDPAK package, which is not quite the same as the DPAK of your IRF part, they give:

(From the LT1965 datasheet, see there for more detail on the test conditions)

At least you can see that getting to less than 29 C/W is somewhat challenging. The only test conditions in the Linear results that achieved that required 4 square inches of copper on both the top and bottom layers.

But again, you can only count on these figures as guidelines, because factors like airflow will strongly influence the actual results in your application.