I am working with a SPARTAN 3E-FT256 on Xilinx 14.1, and have to generate a 25 MHz clock from the onboard 50MHz clock.I am accomplishing this with a Digital Clock Manager.

These are my UCF designations :

NET "CLK_50MHZ" LOC = "C8" | IOSTANDARD = LVCMOS33 ; //GCLK 10

NET "CLK_50MHZ" PERIOD = 20.0ns HIGH 40%; //DCM_X0Y1

DCM Instantiation :

wire clk_ibufg;

wire clock;

wire CLK0_OUT;

IBUFG clk_ibufg_inst ( .I(CLK_50MHZ) , .O(clk_ibufg) );

BUFG clk_bufg_inst ( .I(clock) , .O(clk));

ClockManager1 clock_converter (

.CLKIN_IN(clk_ibufg),

.CLKFX_OUT(clock),

.CLK0_OUT(CLK0_OUT)

);

I am very uncertain about the use of IBUFG and BUFG, but the datasheet seems to prefer the connections ---IBUFG to DCM to BUFG---- for minimum skew.

The warning I get :

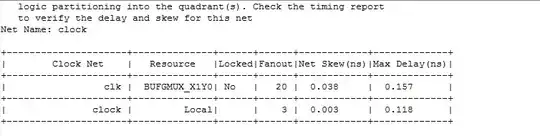

"The following Clock signals are not routed on the dedicated global clock routing resources. This will usually result in longer delays and higher skew for the clock load pins. This could be the result of incorrect clock placement, more than 8 clocks feeding logic in a single quadrant of the device, or incorrect logic partitioning into the quadrant(s). Check the timing report to verify the delay and skew for this net Net Name: clock"

Is there any way to specify which BUFG or IBUFG to use? Why am I getting this warning?