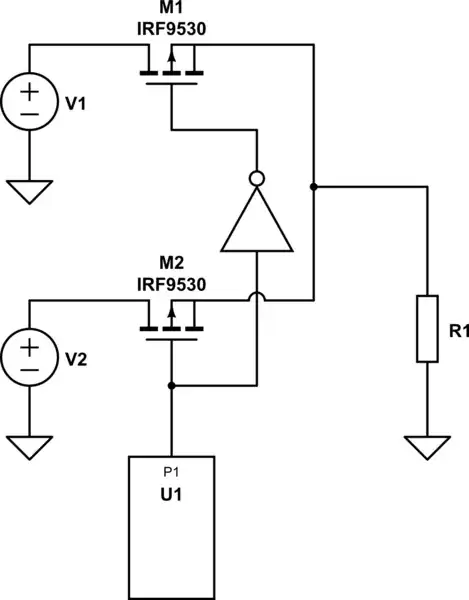

The "error", I* believe, is that you forgot about the MOSFETs's parasitic diode, which won't let you do what you want even if the "inactive" transistors are turned OFF.

For example, below, if Q1 is turned OFF and Q2 is turned ON, D1 will be forward biased and will connect V3 to V1 as well as to R1.

However, if Q1 is turned ON and Q2 is turned OFF, D2 will be reverse biased by V3, so that'll work.

I don't think the scheme will work, in general, since there'll always be one diode forward biased unless the only thing ON is the transistor switching the lowest voltage supply.

By the way, I've posted the LTspice circuit list after the grasphic just in case you want to play with the circuit.

Version 4

SHEET 1 880 680

WIRE 128 -32 80 -32

WIRE 240 -32 192 -32

WIRE 80 64 80 -32

WIRE 80 64 -176 64

WIRE 112 64 80 64

WIRE 240 64 240 -32

WIRE 240 64 208 64

WIRE 336 64 240 64

WIRE 128 112 -64 112

WIRE 128 208 80 208

WIRE 240 208 192 208

WIRE 80 304 80 208

WIRE 80 304 32 304

WIRE 112 304 80 304

WIRE 240 304 240 208

WIRE 240 304 208 304

WIRE 336 304 336 64

WIRE 336 304 240 304

WIRE 336 384 336 304

WIRE -176 400 -176 64

WIRE -64 400 -64 112

WIRE 32 400 32 304

WIRE 128 400 128 352

WIRE -176 544 -176 480

WIRE -64 544 -64 480

WIRE -64 544 -176 544

WIRE 32 544 32 480

WIRE 32 544 -64 544

WIRE 128 544 128 480

WIRE 128 544 32 544

WIRE 336 544 336 464

WIRE 336 544 128 544

WIRE -176 592 -176 544

FLAG -176 592 0

SYMBOL pmos 208 112 M270

WINDOW 0 94 64 VLeft 2

WINDOW 3 69 98 VLeft 2

SYMATTR InstName Q1

SYMATTR Value Si7137DP

SYMBOL pmos 208 352 M270

WINDOW 0 93 64 VLeft 2

WINDOW 3 66 104 VLeft 2

SYMATTR InstName Q2

SYMATTR Value Si7137DP

SYMBOL res 320 368 R0

SYMATTR InstName R1

SYMATTR Value 1

SYMBOL voltage 32 384 R0

WINDOW 123 0 0 Left 2

WINDOW 39 0 0 Left 2

SYMATTR InstName V3

SYMATTR Value 5

SYMBOL voltage -176 384 R0

WINDOW 123 0 0 Left 2

WINDOW 39 0 0 Left 2

SYMATTR InstName V1

SYMATTR Value 3.3

SYMBOL voltage -64 384 R0

WINDOW 3 24 96 Invisible 2

WINDOW 123 0 0 Left 2

WINDOW 39 0 0 Left 2

SYMATTR Value PULSE(10 0 1 1u 1u 1)

SYMATTR InstName V2

SYMBOL voltage 128 384 R0

WINDOW 3 24 96 Invisible 2

WINDOW 123 0 0 Left 2

WINDOW 39 0 0 Left 2

SYMATTR Value PULSE(10 0 3 1u 1u 1)

SYMATTR InstName V4

SYMBOL diode 192 -48 R90

WINDOW 0 -29 31 VBottom 2

WINDOW 3 -31 29 VTop 2

SYMATTR InstName D1

SYMATTR Value RFN30TS6D

SYMBOL diode 192 192 R90

WINDOW 0 -32 30 VBottom 2

WINDOW 3 -32 30 VTop 2

SYMATTR InstName D2

SYMATTR Value RFN30TS6D

TEXT -168 568 Left 2 !.tran 5