I have a question seeking to clarify EXACTLY what happens during a GMII exchange between MAC and PHY. Specifically, regarding the TX_ER signal.

IEEE 802.3 Section 3:

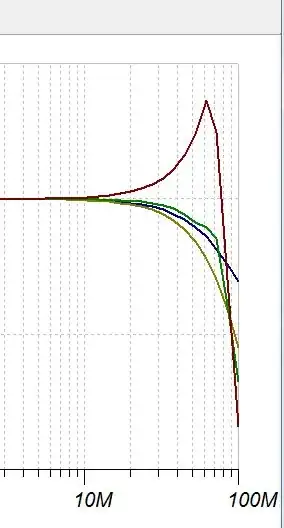

TX_ER is driven by the Reconciliation Sublayer and shall transition synchronously with respect to the GTX_CLK. When TX_ER is asserted for one or more TX_CLK periods while TX_EN is also asserted, the PHY shall emit one or more code-groups that are not part of the valid data or delimiter set somewhere in the frame being transmitted. The relative position of the error within the frame need not be preserved. Figure 35–4 shows the behavior of TX_ER during the transmission of a frame propagating an error.

My Question: When TX_ER is asserted by the MAC (while TX_EN remains high), does the frame still leave the PHY with all other frame bytes still intact, and ONLY the bytes transmitted while TX_ER is high get jumbled? Or does the PHY completely stop transmitting the frame once an error signal is detected?

I am working on an FPGA design that should be able to drop or pass a frame based on its contents, and I am wondering if assertion of the GMII TX_ER signal to the PHY would be considered "dropping the frame" or not.

In the case of the bytes still leaving the PHY, it would seem that the packet would only be "dropped" because the Ethernet FCS would not match the contents of the packet. But the frame contents would still be received by the PHY on the other end, and so if the receiver side had access to the physical layer, the data could be potentially recovered (which is not acceptable in my case).

I have tested this using the network utility iperf, and it appears that the application data does not go through if TX_ER is asserted. However wireshark seems to tell me that there are still valid TCP packets being received, and I don't understand how that is possible if the physical layer CRC doesn't match the frame contents.

Any insight much appreciated.

Thanks!