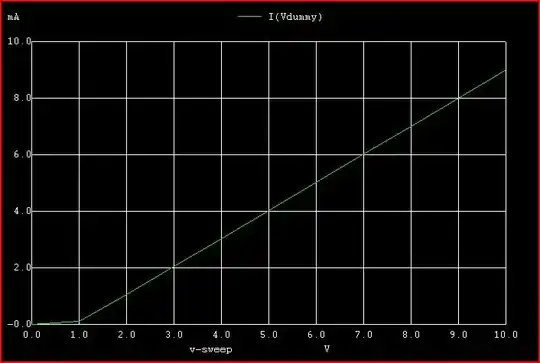

I am trying to design a basic PLL (second order-type 1) to understand its dynamics. I am using Cadence Virtuoso for simulations. I have designed a voltage controlled oscillator that has a center frequency (at Vcontrol = VDD/2) of 16MHz, an XOR phase detector and a passive RC low pass filter.

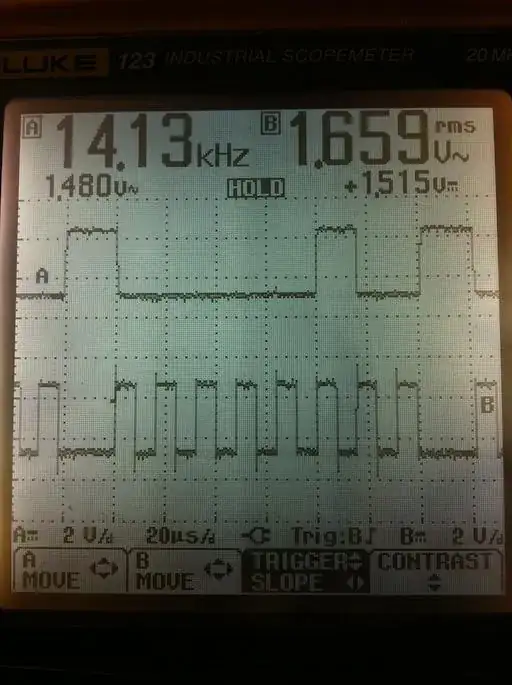

As I've observed, for an input signal of 15-20MHz, the loop acquires the lock.

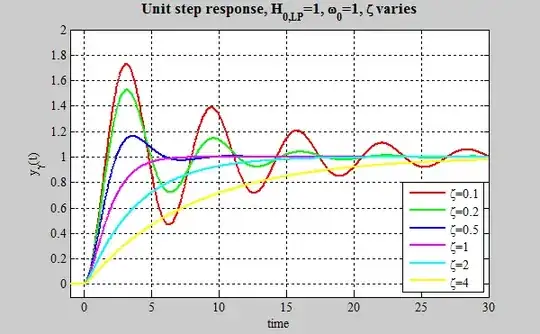

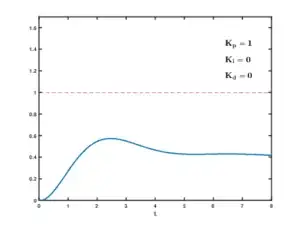

I want to observe how the PLL tracks any change in the input frequency, once the lock has been acquired. Is there any way I could simulate this?

Parametric analysis provides different set of curves for different input frequencies. This does not tell you much about the response of loop. If I could observe, once the loop is locked, how the output frequency tracks the input say for a step change in input frequency.