Any better/more reliable ideas?

at least a few ways:

1) use a bandpass filter and then adc the output to detect the presence of certain frequencies. it is fast but has a higher part count and needs more real estate;

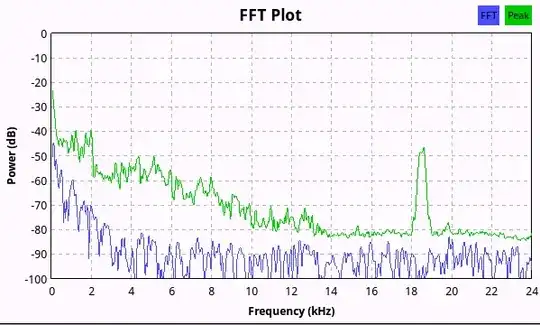

2) use of digital processing: fft could be one approach. the accuracy / speed is dependent on a lot of factors. But over all, what you want to do is doable.

3) somewhere in between. for example, there are algorithm that can detect the amplitude of a particular frequency -> essentially fft at a fixed frequency. there are algorithm that's iterative, vs in batch mode, to speed up the execution, etc.

I think the big picture is that it is doable. but there are challenges and shortcuts to deal with.

edit: here is an example of the third approach.

it relies on a simple fact that if you integrate, over a long period of time, the product of the input signal and a reference signal (of a known frequency), the product approaches a constant * the number of data points.

so what you could do is to say sample at a known frequency, and multiple the adc results with a sine table synchronized with the sampling frequency. if that sum of the product is substantial, the known frequency is present in the input signal.

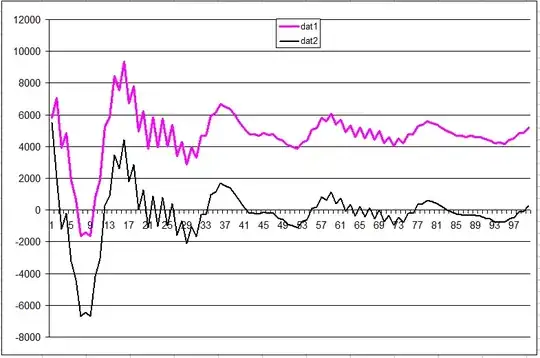

here is a numeric example. two input signals,

sig1 = -123 + 1000 * sin(2pi*f*0.5+phase) + 100 * sin(2pi*f+phase) + 1000 * sin(2pi*f*2+phase) + 10000 * sin(2pi*f*3+phase) + noise;

sig2 = -123 + 1000 * sin(2pi*f*0.5+phase) + 000 * sin(2pi*f+phase) + 1000 * sin(2pi*f*2+phase) + 10000 * sin(2pi*f*3+phase) + noise;

notice the difference between sig1 and sig2: sig2 is missing the base frequency -> its magnitude is set to 0 to simulate the absence of the base frequency.

also, both sig1 and sig2 contains lots of harmonics, even at the magnitude much higher than the base signal. our job is to identify the base signal among all the noise.

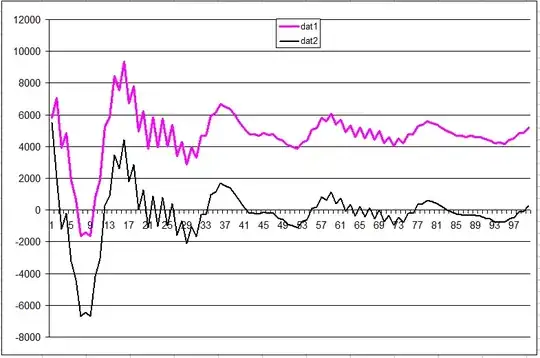

the following chart plots dat1 = sig1 * sin(2pif) and dat2 = sig2 * sin(2pif).

See for yourself, :)

the chart is normalized to the number of samples integrated over.

after about 20K samples, the difference between the two becomes fairly clear.

other fancier algorithm also exists, like ieee1057 or 1241. both can be much faster than fft if the frequency of the signal you want to detect is known.