It is better to have multiple vias. Ideally, one via per cap. It actually makes a huge difference for decoupling. Now, for a microcontroller circuit you won't need to decouple 100's of MHz, so it all depends.

For really high speed applications the track from the cap to the via must be kept as short as possible. That is to provide a good connection for RF to ground. It actually makes a big difference. Did you know that if you have a via that is 0.1 mm from a 0402 pad you get half the bandwidth than if you had the via on the pad. This should illustrate why you must keep via distance to a minimum.

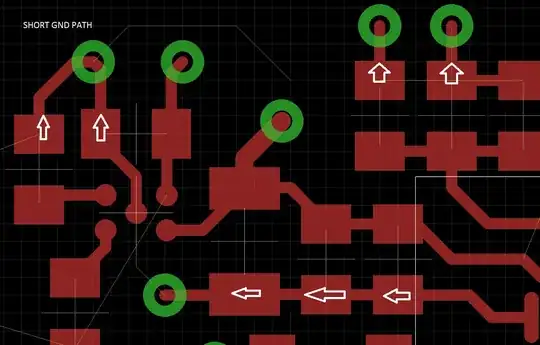

Also, you can create large current loops, if you use a single via, because you are restricting the current to the conductor. High frequency current travels like this in a ground plane:

By high frequency I mean 1 MHz.

It minimizes the loop area by following the top conductor. So you should aim to get the current on a plane as soon as possible. If you are worried about contamination, keep digital/analog traces apart. 95% of the current is within 3 track widths on the ground plane. Also, stay away from the edge of the plane. There is current on the edge, just like near the conductors.

By high frequency I mean 1 MHz.

It minimizes the loop area by following the top conductor. So you should aim to get the current on a plane as soon as possible. If you are worried about contamination, keep digital/analog traces apart. 95% of the current is within 3 track widths on the ground plane. Also, stay away from the edge of the plane. There is current on the edge, just like near the conductors.

Edit

Also, keep in mind that capacitors become inductive at lower frequency than we expect. Here are some typical Murata curves:

Here is a good article about decoupling techniques.