Should I guard a PLL loop filter against current leakage with a pour? If so, where can I connect the guard plane?

As an illustration: I use an IC in need of an external PLL-loop-filter connected to the charge pump (a MAX2769). The manufacturer recommends to use a C-R-C-network as follows: (the DNIs are not installed, the installed caps are silver mica type from Cornell Dubilier).

(the DNIs are not installed, the installed caps are silver mica type from Cornell Dubilier).

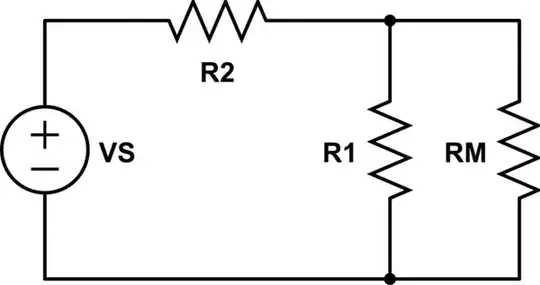

As you can see, there is a 1M (or 100M?) resistor to a net called PLL_FILTER_FENCE. This network is used to pour a plane around the components like this: This pour is intended to minimize current leakage from the components. As you can see, space does not allow for a plane that also encloses the IC pad. The plane will also introduce an additional filter pole which should not affect PLL performance.

This pour is intended to minimize current leakage from the components. As you can see, space does not allow for a plane that also encloses the IC pad. The plane will also introduce an additional filter pole which should not affect PLL performance.

Will this be helpful at all, as there is no low impedance source to connect the guard to?