I'm trying to figure out a way to use the Power Good outputs of several stages of voltage regulators to sequence and monitor a board powering several FPGAs. I've done this easily before with a microcontroller, but this is not allowed (!) in this design.

I have setup a primitive sequencing scheme with RC-delays and comparators which turns on the regulators in order. The problem here is I need to monitor several Power Good pins which are tied together.

As I understand it the Power Good pins are open drain pins which are pulled to ground if VOUT of the regulator is below (or over) a certain level. Unfortunately (and obviously) they don't pull to ground if there is no input voltage present at the regulator input. So the input to the comparator needs to be pulled up, possible to parallell and only assert when all Power Good pins are OK.

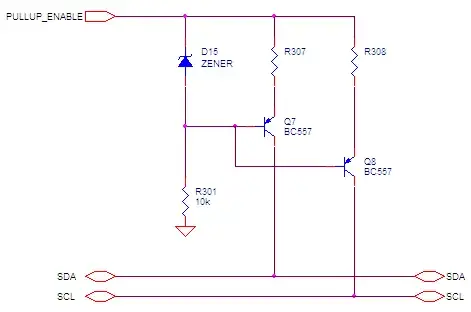

My current idea of solving this is the below transistor circuit: When the first regulator turns on, its VOUT pulls the PG pin which should be low until VOUT is OK. The transistors connected to the PG pin are set up so they ground the line which is paralleled to other regulators PG during the startup, and releases the global PG only when the regulator PG is OK. When all Power Goods are released this will trigger the enable pins of the next stage of regulators.

Will it work?

simulate this circuit – Schematic created using CircuitLab