TL;DR

A circuit is presented based on a regulator topology, stable into any capacitive load, which includes a diode in series with the output current. The voltage developed across this diode is nominally the log of the current, which allows a very wide range of current to be measured with a single voltage range. Excellent dynamic stability has been demonstrated in simulation.

At low current, the circuit is noisy and slow (no big suprise). The present results show about +/- 5% rms noise at low currents, for settling times of 10uS for currents of 1uA and above, increasing to 1 second settling time for currents down to 1nA.

/TL;DR

I suspect you don't need high accuracy. You only think you do because of the huge range from nA to 500mA. Obviously +/- 1nA at 500mA would require collossal accuracy. I suspect that +/- 10% at 500mA simultaneously with +/- 10% at a few nA and a single range to cover both without switching would be useful.

The initial thought, that I threw down as a suggestion initially, is shown at the bottom of the post for reference.

Unfortunately it has a fatal flaw. While it can indicate 1nA well enough, as the current suddenly increases, the opamp output doesn't initially move, due to both its internal compensation and C1. As a result, the output voltage drops by over 1v (needed to get the current flowing through Q1 and D1) for a moment, which would severely embarrass any MCU being supplied by that line.

The 'solution' is to incorporate the MCU rail decoupling capacitance into the analysis. However, extra C on the MCU line provokes instability, as it is in shunt with the opamp inverting input, and practically uncompensatable over a the wide range we want.

So the next thought was 'this is basically a transimpedance amplifier, albeit with a very non-linear feedback resistor, how are they stable?' A quick search for those brought me to Bob Pease's article (Nat Semi's RAP, Bob Pease - must reading for any analogue designer. If you take nothing else from this answer, dig out and read some of his stuff!)

It was quickly apparent that the assumed capacitance on the op-amp inverting node, although big compared to pF, was very small compared to the 10uF that we might find on a VCC line, and the high speed tweaking assumed a constant feedback resistor, so this topology was a non-starter.

So then I thought, if we are not going to brown-out the MCU when the current changes, it must behave like a regulator. I recalled the tantalum versus ceramic output capacitor issues of LDOs. Architectures that rely on the half ohm ESR of a tantalum to be stable are not stable with ceramics. When the topology is changed to tolerate ceramics' zero ESR, they can tolerate any large value above the specified minimum.

In order to cope with a large output capacitor, it is designed to be the dominant pole, with an output current source turning it into an integrator, keeping the rest of the control chain with less than 45 degrees phase shift. Once that flip has been made, the output capacitor can be any size larger, and the LDO will still be stable. The output capacitor of the regulator provides all the voltage hold-up during a current change event.

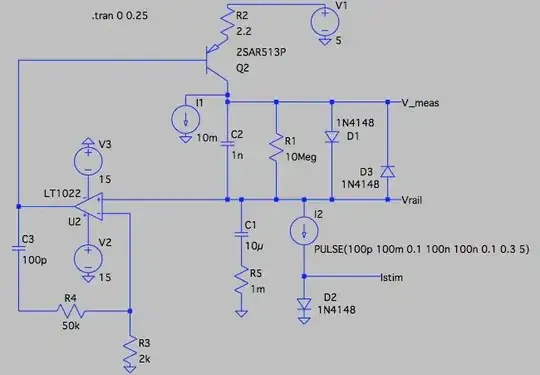

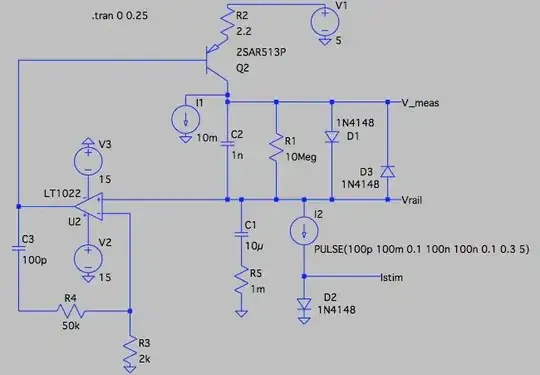

Now I searched for LDO app notes. This is the new design as a result. It is broadly similar to the original one in DC concept, but is built round the output capacitor, and uses the tricks employed by LDOs designed for ceramics, to get sufficient stability.

Analysis

Q2 is the series pass PNP device, configured with R2 to be current output. That particular type is 1 Amp, 200 hfe 150, 50v, 400MHz ft fairly cooking-grade part that was in the LTSpice library. I1 biasses it to a nominal 10mA, to reduce the delta V required when suddenly required to increase current from zero, and to provide a substantial current sink to cope with a sudden reduction in current output.

D1 is our old friend the non-linear element across which the output current develops the log voltage. I've used 1n4148 as it was in the library. It's joined by R1, to define the bottom end of the current range (10mV for 1nA), D3 to catch reverse voltages when the current suddenly decreases, and C2 as it improves stability and output overshoot. Note that if the 1N4148 is replaced by beefier 1n400x types, their higher capacitance will be completely absorbed by C2, so are well enough modelled for stability.

I would have modelled a TL071. I first tried an LTC1150 which had a GBW of 1.5MHz, but struggled to get reasonable stability. I then switched to the LT1022 shown. This is a bit quicker at 8MHz GBW, but there are many much quicker parts around.

The network around it includes R3 to sense 0v, C3 for stability, and R4 to add a zero to C3, as suggested in LDO app notes. With these values, arrived at by hope'n'poke, it's already not bad. I'm sure it could be better with a bit of proper analysis. Rather than using a yet faster unity gain stable amplifier, it should be better to use one that's decompensated.

It certainly looks stable enough for the purpose. Anybody building this circuit to use in anger may find some more unmodelled parasitics that reduce stability, but I would suggest they start with a yet faster amplifier to give themselves some more elbow room.

I2 provides the time dependent current loading for the demo. As you can see from the parameter string, it's slewing 100pA to 100mA with 100nS risetime (so changing current on in one cycle of 10MHz), and back again. The diode D2 provides a convenient way for the simulation to show the log current, and is no part of the target circuit.

When doing simulations, I prefer to have all the 'action' around 0v, so for the rails of -5, 0v and +5v shown here, read 0v, +5v and +10v respectively for the OP's application.

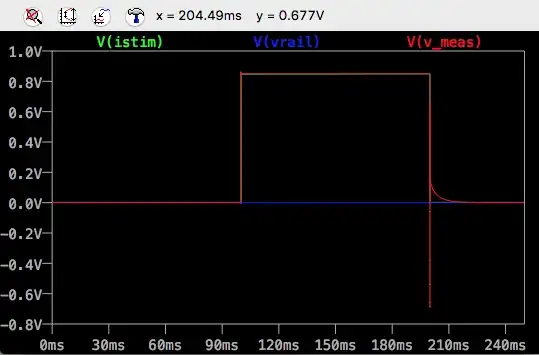

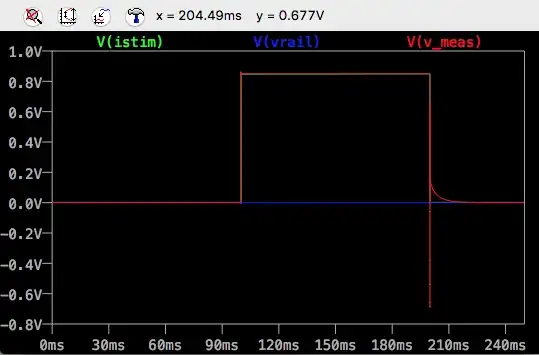

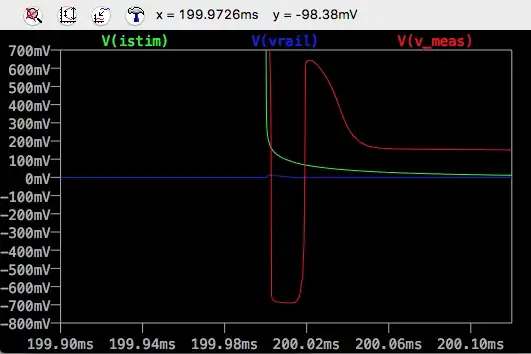

This is the overall transient plot

The initial DC value of the output voltage is 0.5mV for 100pA, and when I go from 1nA, it's about 5mV, so we have sensible discrimination at, and below, the 1nA level.

There is a slight overshoot of the measurement value when the current increases.

The slew hits the diode limits when the current decreases. There is also a 20mS reading tail when switching down from 100mA to 100pA, I don't know how to improve that, perhaps somebody has a suggestion. The tail is still present when switching down to 10nA, but when switching down to 100nA or more, the tail is absent. For this application, I would imagine that's OK.

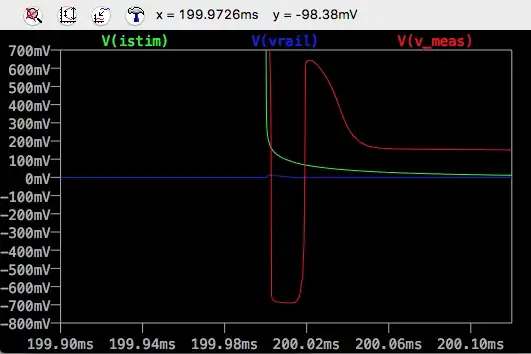

In the next three plots, we look at the all important output rail voltage stability.

On the increase from 100pA to 100mA

The up-going rail transient is only 12mV, and dead beat. You won't find many commercial LDOs delivering that sort of performance for such a violent current change.

and on the way back down again to 100pA

Without D3 to provide reverse conduction, Vmeas would swing to the -ve rail for a while rather than to -0.6v.

The down-going rail transient is also limited to 12mV. You can see the rate-limited downwards slew which is the result of the I1 current sink.

I'm not going to say it's a proof of principle, but I think it is a very good proof of plausibility. The simulation includes a lot of parasitics, Q2 Miller C, the opamp's compensation, and with performance rivalling an LDO, I think that's a pretty good basis from which to start developing something that can power an MCU, at different currents, reading over a large range.

This shows Vmeas as the output. As indicated in the original post, thermal accuracy will be improved if it is measured with respect to another diode at the same temperature. Vmeas is a low impedance output, so this is very straightforward to do with a simple differential amplifier.

As before, replacing R1 with a lower value resistor will give a more accurate, linear range output, for voltages for which D1 is not conducting.

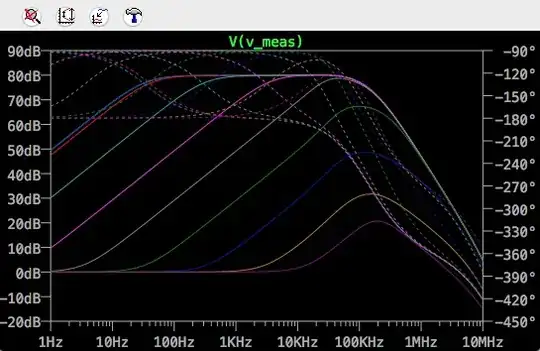

Noise issues

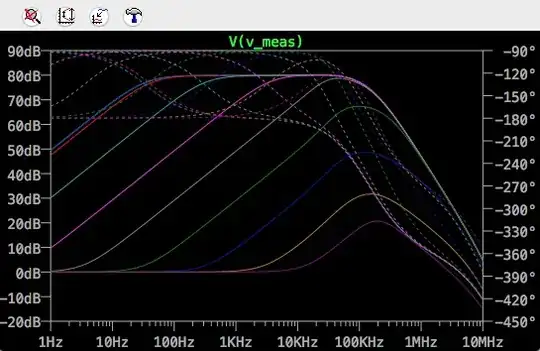

Now that a stable circuit has been developed, we can start to look at noise. The following graph shows the gain from op-amp input, with a 1nF capacitor fitted at C2. The curves cover 100pA to 100mA. The 100pA and 1nA curves are indistinguishable at bright blue, and very close to the red 10nA curve. 1uA is pink, 1mA is dark blue, the 100mA curve is lowest as purple.

Using LTSpice's .noise simulation, and using .measure to integrate the output noise over a bandwidth of 10mHz to 10MHz, using a 33nF capacitor for C2, resulted in a relatively constant 2mV rms noise for currents 1nA to 100uA, with noise falling as currents increased to around 100uV rms at 100mA.

The penalty of the increased value of C3 was increased settling time following a step reduction in current. The time to within 1mV of the final value was approximately 10mS to 1uA, 60mS to 100nA, 500mS to 10nA, and 900mS to 1nA.

The present op amp, LT1022, claims several 10s of nV at 1kHz. Bob Pease's transimpedance amplifier article referred to earlier suggests that 3nV is feasible with a low current FET input, using discrete low noise FETs as the front end to a composite amplifier. Using such an improved opamp should reduce the noise levels by an order of magnitude.

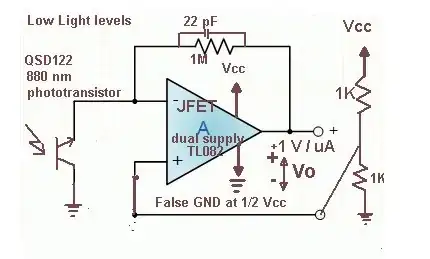

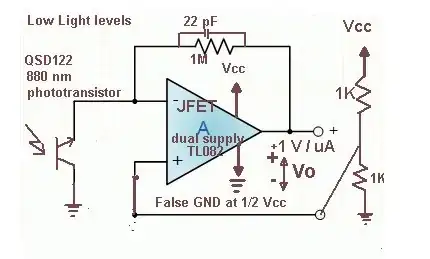

This is the original suggestion, for reference.

simulate this circuit – Schematic created using CircuitLab

The opamp will servo the current through Q1 and D1 to maintain the output voltage at 5v, so your MCU is always seeing its correct operating voltage.

The voltage you measure between the two diodes is proportional to the log of the ratio of D1 current to D2 current. While you can work with the voltage across D1 alone, it is temperature dependent. This method uses D2 to compensate that dependence.