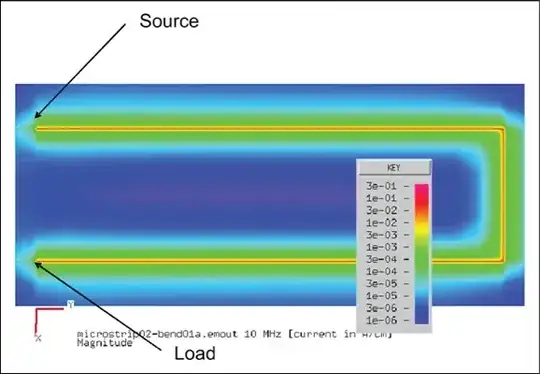

It is known that the return current starts following the conductors as the frequency increases:

So as long as one keeps the distance between the conductors large enough there shouldn't be the need for local ground planes.

So as long as one keeps the distance between the conductors large enough there shouldn't be the need for local ground planes.

Why then some people suggest the use of localized ground plane, like the answer to this question: https://electronics.stackexchange.com/a/15143/4512 It is suggested that the ground plane will work as a patch antenna.

But the current on the ground plane will closely follow the conductor, resulting in a small loop area. And the generated magnetic field is given by Faraday's law: $$\oint_{\partial A} \mathbf{E} \cdot d\mathbf{r} = - \frac{\partial}{\partial t} \iint_A \mathbf{B} \cdot d\mathbf{s}$$

By using a smaller localized ground plane the generated EM radiation will be the same, because the loop will be the same. Additionally, the localized plane can introduce plane resonance, and one needs to avoid crossing it with high frequency signals.

So, what are the benefits of using a localized ground plane?