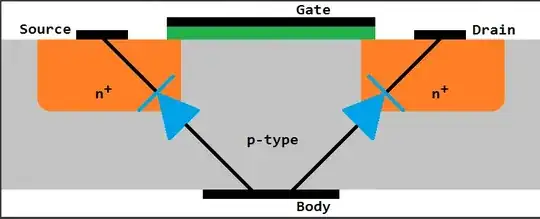

Some NMOS's come with a substrate/bulk/body terminal so the "Source Voltage" referred to in literature then Substrate Voltage. Say then we short the gate to the drain and have the substrate take the input. We would then use this in the same NMOS V_DS bias. The higher voltage will go with drain and lower voltage to source.

Well, what's the difference now? Since N-channel MOSFETs need a gate-to-substrate positive differential relative to voltage threshold to go active, then in this configuration, when we pull the substrate terminal, relative to the threshold, the NMOS activates. Leave it within threshold or negative (above the gate), it doesn't go active. Effectively PMOS, though, in terms of Physics, the charge carriers moves from the side with lower voltage (source), instead of the higher one (drain).

Is there a big hole in my logic here? Are there any practical considerations that was not mentioned?

I ask the latter as I'm not even sure if driving from the substrate side will give decent and similar Transconductance. It's usually manufactured just as a wide plane at the back.

On that topic, wouldn't it have been better if we optimized the substrate also so that we can attach a terminal there and expect symmetrical result as with driving from gate? Then we'd have a 2 port monolithic/discrete semiconductor.