That's not a protection device, if you intend "protection" as something that prevents the chip to die, but it serves as a so-called bypass capacitor.

It acts as a reservoir of energy whenever the chip draws pulses of current when switching occurs. If the power rails were truly ideal connections, with no resistance nor inductance, bypass caps wouldn't be necessary.

Since the rails have some resistance, whenever the chip absorbs a sudden pulse of current, a corresponding voltage drop develops along the rail, risking to bring the rail voltage out of specs. The bypass capacitor reduces this risk in a way similar a filter capacitor after a bridge rectifier reduces the ripple of a rectified voltage.

In other words, bypass caps help keep the voltage of the power rail constant at the chip terminals, which is what is needed for its correct operation.

Note that bypass caps need to be placed near the IC they are meant to "protect", in order to be effective. Here "near" means that between the terminals of the cap and those of the chip there must be the least distance possible along the copper traces, in order to minimize the resistance (and the inductance as well) that is not bypassed.

Dave Jones, of EEVblog fame, has made a nice tutorial about bypass capacitors (EEVblog #859).

EDIT (prompted by a comment by Floris)

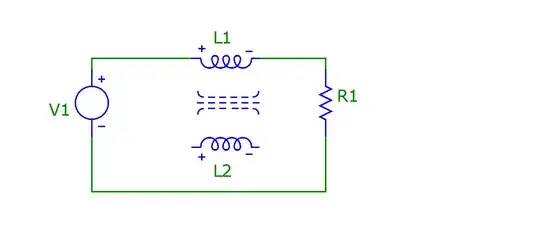

In the explanation above I focused on the voltage drop caused by the resistance of the rails because it is the easier to understand, especially for a newbie. To avoid giving a false impression, though, I must emphasize that the resistive effects are not the principal cause of voltage drop during current spikes. The principal culprit is the inductance of the rails, especially in high performance circuits, where switching is very fast. In fact, an inductor of inductance L presents a reactance \$X_L = 2\pi f L\$ (if you don't know what I'm talking about, see it as a sort of "AC resistance") that is proportional to the frequency. Therefore current spikes with higher frequency components (i.e. having steeper edges) will cause a more substantial voltage drop.