So it looks like the IO Warrior56 is likely a Cyprus microcontroller with pre-assembled firmware. It states that outputs are open-drain, with 4-8kΩ internal pull-up resistors. A few notes about this and USB:

- All micros can be damaged if the voltage on any pin rises above or below it's power rails (here by \$\pm \$0.5v.)

- USB will likely limit the total current available to 100mA. A 500mA "high power" USB mode may be available, but not all hosts support this.

- If all 50 I/O lines of the IOW56 were driven low with worst-case 4kΩ internal pull-up resistors, that would draw 5v/4k = 1.25mA * 50 = 62.5mA from USB. So the maximum current in addition to this USB can source in standard mode reliably is 100-62.5 = 37.5mA or 0.75mA per pin.

- \$I_{IH}\$ and \$I_{IL}\$ of the 74LS367 are 20µA each. 20µA*50 = 1mA, so the loading here is fine for 100mA USB operation, if these are the only things connected to it.

- One 74LS367 maximum supply current is 24mA, so multiples of these cannot be powered from USB in standard-power mode.

So I'm assuming either high-power USB mode is being used, or the 74LS367's are being powered separately.

The 74LS467 output stage (page 2) is a typical totem-pole, with 40-50Ω source resistance shown, but more like 2kΩ effective. Input stages are typical diode-clamped, with a pull-up resistance to Vcc. Maximum on most pins is 7.0v to -1.5v.

The SN74LS367A is limited to 2.6mA source, and 24mA sink current, which does not meet your 10mA requirement. If a high-pass transistor is used, then you risk coupling this 60v directly into Vcc, likely destroying everything.

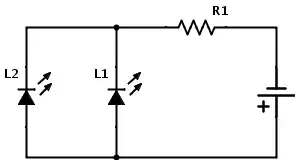

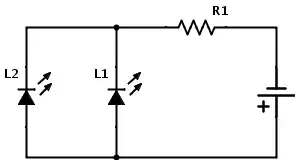

If whatever these outputs are driving is normally fairly high-impedance, then the following might work to clamp +60v to -60v. Fuse is not modeled. This does reduce the drive current slightly, and the 1N5338B's also introduce some small amount of capacitance (not specified in the datasheet) which will slow down fast transitions slightly.

Note that this will dump up to 1A per pin into the 5V supply if fuses are not used (which would be ludicrous.) Place a 60v-capable alarm across the fuse, and that can indicate a fault. A PTC Polyfuse may be an option, however they have on-state resistance, a higher resistance after tripping, and limited power-handling capability.

As @winny suggests, another good idea is to add a high-side current monitor to the 60v supply. Feed this signal into a window comparator to set the normal operating current range of the DUT, and set a level where current is too high. Once the "too high" level is reached, shut down the power supply and indicate a fault. Details about such an approach should be asked in a separate question.