I have seen this question and removed the "#.." part of my code to introduce delay, since my code will ultimately run on hardware.

Anyway, I am trying with counters and not able to introduce the required delay of n clock cycles. Here is my code:

`timescale 1ns / 1ps

module SyncDelay( clk_27,vsync,vsync_o);

input clk_27;

input wire vsync;

output reg vsync_o;

reg[2:0] cnt=0;

always @ (clk_27)

begin

if(cnt > 3'd4)

begin

vsync_o = vsync;

end

else

begin

cnt = cnt + 1;

end

end //always

endmodule

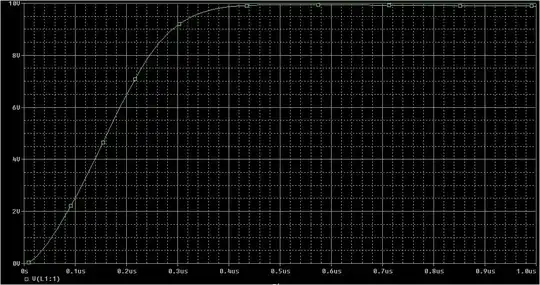

This is what I'm getting:

vsync and vsync_o have the same values at all instances. Instead, I want vsync_o to lag with a delay of n clock cycles.

EDIT:

With the code:

`timescale 1ns / 1ps

module SyncDelay( clk_27,vsync,vsync_o);

input clk_27;

input wire vsync;

output reg vsync_o;

reg[2:0] cnt = 0;

always @ (clk_27)

begin

if(cnt > 3'd4)

begin

vsync_o = vsync;

cnt = 0;

end

else

begin

cnt = cnt + 1;

end

end //always

endmodule

I get: