I'm trying to interface this clock (32.768kHz Ceramic Surface Mount Crystal Oscillator datasheet), but I'm confused as to what to do with the tri-state pin. What is it's purpose in the oscillator and should I care about it? Can I just leave it unconnected or pull it to ground?

-

What is "this clock"? What chip are you talking about? With the information you have given so far, it is impossible to answer (or even make an informed comment) on your question. Yes, sometimes clocks are tri-stated. For example, this is used in I²C for [clock stretching](http://www.i2c-bus.org/clock-stretching/). – tcrosley Jun 12 '16 at 22:23

-

@tcrosley: An I2C clock is not tri-state, it is just open drain, as driving strongly high is just plain illegal. You can use a tristate buffer to produce that, but then the clock should be tied to the enable pin of the buffer, with the input tied low. But the configuration here has the clock signal fed to the tristate buffer's input. – Ben Voigt Jun 13 '16 at 00:50

-

1@BenVoigt You're right, I was mixing up tri-state and OD. Now that the chip has been identified, the only reason I can see for this functionality would be to allow more than one oscillator to be connected in parallel driving another chip. Odd. Never seen this before. – tcrosley Jun 13 '16 at 04:08

6 Answers

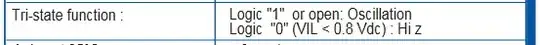

There is a line in the Parameters table on p.1 of the datasheet, which describes the function of the Tri-state.

It's a kind of an enable-disable pin.

- If Tri-state pin is logic "1", then oscillator is connected to the output pin. Same happens if Tri-state is left unconnected (there's probably an internal pull-up).

- If Tri-state pin is logic "0", then oscillator is not connected to the output pin, and output is floating. The fact that it's floating may be useful if you need to switch between several clock sources. You would enable one of them, and Tri-state the others to prevent contention between multiple outputs.

edit:

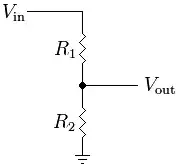

Here's an example where an enable/disable with tri-state is used with an external clock source. When connecting external clock source to J1, the J2 jumper should be installed. The resistor R1 protects from a direct short between clock outputs.

(schematic from p.22 in this user guide and datasheet for that oscillator)

- 37,739

- 17

- 97

- 230

There are already a slew of answers that explain the functioning of the enable pin on the oscillator part. Let me provide some reasons that pin can be useful in real world situations.

- Sometimes a circuit board is tested with an automated test fixture with pogo pin test points all over the board. In such test environments the clocks for the circuit are often supplied from the tester equipment so it is necessary to shut off on board oscillators so that the tester clocks can drive the board.

- In similar test situations like #1 above the test fixtures with pogo pins have 100's of long wires connecting the test fixture to the test equipment. On onboard oscillators can create a problem with overall noise if they are allowed to run. A test point access to disable the oscillators can be beneficial to shut off the oscillator.

- Some board designs may have logic tied to the oscillator output. That logic consumes power when the clocks are running. If the design is one that needs to save power by going to sleep for periods of time a GPIO can be attached to the oscillator enable to allow it to be disabled when entering the sleep state.

- There are some complex ICs that have multiple power rails that must be sequenced on and off to ensure proper operation. There are cases where sequencing requirements also require that clocks to the part are held off until the appropriate point in the power sequence. Clocks provided by oscillators can use the enable pin to hold it off till the right time.

- 56,889

- 3

- 70

- 138

-

Given that the OP is asking about what to do with the tri-state pin, you might want to describe what to include in the schematics to design for testability (i.e. use #1 & #2). For example: have a resistor between whatever is driving the pin (be that logic or a power rail) and the pin with a test/probe point on the net between the resistor and the pin (assuming you don't automatically include probe points on all nets). While the other cases you mention require design too, they are more complex and would have the designer already thinking about how to accomplish the desired function. – Makyen Jun 13 '16 at 01:17

-

@Makyen - I said "Let me provide some reasons that pin can be useful...". My intent is not to design it. – Michael Karas Jun 13 '16 at 05:05

When the tri-state pin is High or not connected, the oscillator will produce its normal output. If the tri-state pin is connected to Ground, the oscillator output will be high impedance, effectively disabling the output. This is described in the second-last line of the "Standard Specifications" table.

You might want to use this feature if you wanted to switch between two or more clock sources.

- 57,014

- 1

- 48

- 127

-

2_THIS_ "if you wanted to switch between two or more clock sources." !!! – placeholder Jun 12 '16 at 22:34

It's an enable pin. From the data-sheet.

Tri-state function:

Logic "1" or open: Oscillation

Logic "0" (VIL < 0.8 Vdc): Hi z

Ground the pin, and the Oscillator stops ticking or the output disabled. Same difference in practice, but without the warm-up instability time that it would take if power was cut instead.

If you don't need to use this feature, the normal usage is to tie it high, or leave it open/unconnected, for the oscillator to keep clocking.

The use of the phrase "Tristate" here is odd to the point of obfuscation, but seems like technically correct.

-

The clock may still tick internally, but it won't drive the output pin. – Peter Bennett Jun 12 '16 at 22:26

-

@PeterBennett I was rewriting that as you commented. Great minds think alike. – Passerby Jun 12 '16 at 22:31

-

? - Tri-state is exactly that, either high or low or floating (Hi-Z) - absolutely no obfuscation. – placeholder Jun 12 '16 at 22:33

-

@placeholder the typical phrasing would be "enable" or "disable" pin. I have yet to see an IC that calls something like this a "Tristate Pin" – Passerby Jun 12 '16 at 22:35

-

It is Tri-state because that is exactly what is needed, see @PeterBennett 's answer. – placeholder Jun 12 '16 at 22:38

Figure 1. Extract from datasheet.

The term "tri-state" is used to describe outputs which can be:

- Low / off / 0 V.

- High / on / V+.

- Disconnected or floating.

Hence there are three states.

In this case the datasheet shows us that the chip will oscillate when the tri-state pin is at logic 1 or open circuit. If it is pulled to logic 0 (less than 0.8 V DC in this device) the output will be disabled and present a hi-z (hi impedance) to the rest of the circuit. i.e., It will appear to be disconnected.

- 168,990

- 12

- 186

- 385