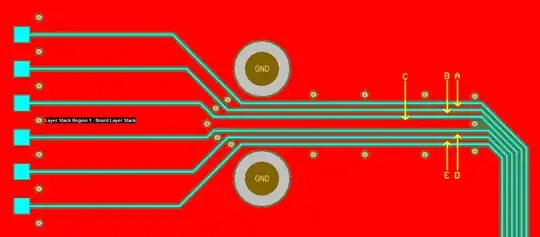

I'm trying to understand the effects of polygon pour fills when high speed line transitions might occur. Consider the fabricated case example below:

In this example the tracks (colored in light blue) were set as much apart as possible on the left of the board, but they had to be taken closer together to fit through the big pad holes. The red fill is the ground polygon pour. Notice that this is a fabricated example that has many other problems unrelated to my question.

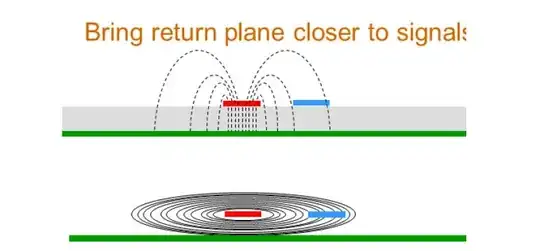

For the sake of the argument, all lines are single ended (like UART, SPI, I²C, etc.) and may have transition times of 1~3 ns. There is a continuous ground plane below (0.3mm distance) but my question is specifically about the ground pour on the top.

In case C the polygon pour was able to penetrate to a place with enough room to place a second via connection, so the ground trace is properly conencted to the plane below. However, in cases A, B, D and E the pour made as far as it could with no space to place for vias, leaving GND "fingers".

What I'd like to know, disregarding other routing considerations, is whether "fingers" A, B, D and E should be removed or perhaps they contribute to reducing crosstalk between the tracks. I'm concerned that ground noise could make those "fingers" good antennas and produce unwanted EMI. But at the same time I'm reluctant to remove them for the possible crosstalk benefit they may have.

EDIT

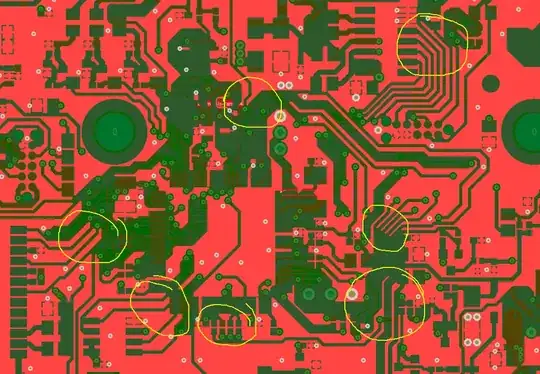

For a diferent case example, consider this picture:

Fan-out from each IC imposes a reality where many of these fingers are unavoidable, except if we get rid of the GND pour entirely on that section. Is the latter the proper thing to do? Is the GND pour beneficial or rather innocuous as long as it is a GND fill?