I want to drive numerous chips on several different PCBs with SPI from a microcontroller over FFC cables.

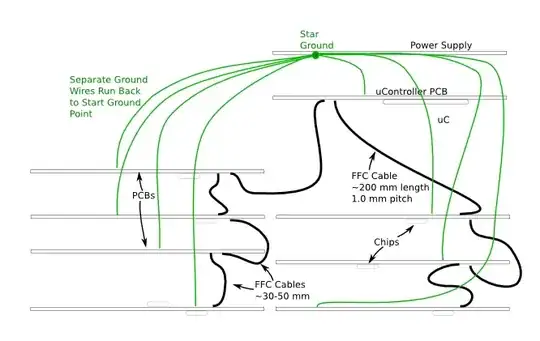

Here is a crude diagram:

UPDATE: Green wires are ground scheme

I have never attempted such a layout and someone has warned that capacitance could be a major issue. As illustrated, there could be 5-10 chips (depending on the combination of boards used) on the digital bus.

The cables are are 8 conductor, 1.0mm pitch, 0.27mm thickness, 1.2A, 60V (like Molex 15267-0237). The pinout of the cables will all be the same since all of these lines are to be connected together to the SPI pins on the uC.

So for example, in the above illustration, the SCLK line would be connected to 8 chips on ~600 mm of cable.

So is this even possible? Or is the combined capacitance of 8 inputs and 600 mm of cable going to destroy my data signals?

Is there anything I can do to limit problems?

I was thinking about a pinout for the cable like:

Cable - uC

------------

SCKL - SCK

SDI - MISO

SDO - MOSI

LE3 - D1

LE2 - D2

LE1 - D3

VL - 5V

RST - D4

Ground wires will run separately from each board to a central point next to the bypass caps of the power supply.

I was thinking that maybe if I put VL between SCLK and SDI and RST between SDI and SDO might help limit crosstalk but I don't suspect that will help with the overall issue of parasitic capacitance.

Fortunately none of this has to run at terribly high speed as it will all be ultimately interfacing with a human being. So 2MHz would be just fine and I suspect 125 kHz might even work.

Ideas?