I have been recently working on different types of MOS amplifiers and the following are my main doubts,

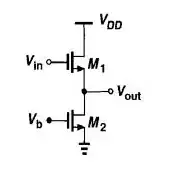

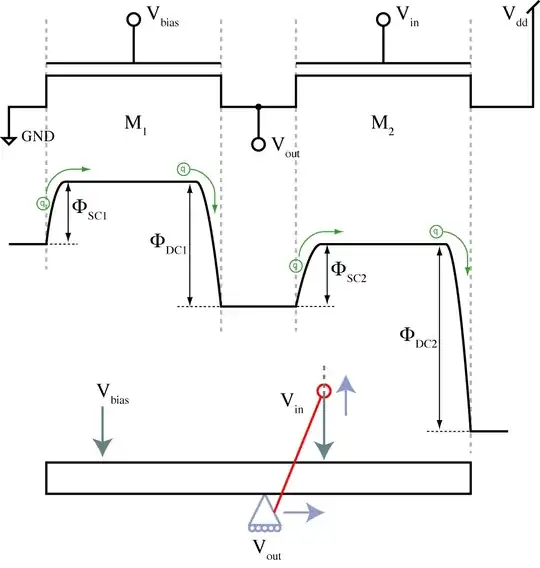

When we have a high gain stage such as the common source stage we use the output of this stage as an input to a common drain stage. What makes the common drain stage so special? I know that they charge capacitors in a much quicker rate (slew rate) compared to the common source stage but is there an intuitive way to understand what makes the common drain stage good for this?

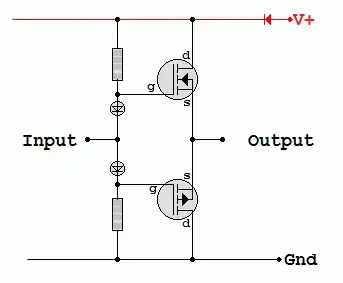

In terms of slew rate is the push pull stage (with the distortion effect corrected) a better option compared to the common drain stage as the final output stage?

Common drain stage <----------> Push-Pull stage