As a newcomer to PIC programming, I am looking for some thoughts on how to implement SPI between a master and slave MCU the most efficient way.

The purpose of this system is to provide an extremely flexible way to 'map' up to 32 individual output pins of the slave MCU to any one of the 32 input pins of the master MCU, using a software-configurable 'matrix'.

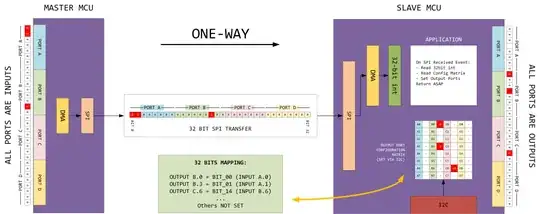

To make things a little more clear, I added a drawing below:

Some another MCU (not in the drawing) manages the port mapping setup and transfers this information to the slave MCU as a 'port matrix' via I2C.

In the drawing example, slave output port B, bit 0 (B.0) should be mapped to master input pin A, bit 0 (A.0) Furthermore, output B.3 should map to input A.1, and output C.6 should map to input B.6

So when master pin A.1 goes high, slave pin B.3 should go high too. From an application point of view, that should be staight-forward.

But what would be the most efficient way to read 32 bits from 4 ports on the master, and have them represented on the slave as a 32bit integer for the application to provide the mapping to its output ports?

SPI clock should at least be 2MHZ to be functionally acceptable. Is DMA a solution here? Can such transport solution be interrupt/event based in order to keep the CPU from polling stuff? Target MCU's are PIC32MX795.

I could definitely use some hints to get this communication going.

Thanks in advance!